Datapath PowerPoint PPT Presentations

All Time

Recommended

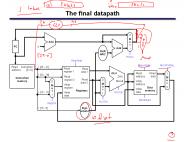

the set of control signals. In our older datapath: ... IR: Instruction Register. MicroProgram Counter. Control word. Next MicroInstruction Address ...

| PowerPoint PPT presentation | free to download

Show any necessary modifications in the multicycle datapath and control figures ... We have to get the second operand from memory before activating the ALU. ...

| PowerPoint PPT presentation | free to download

Laxmikant Kale. http://charm.cs.uiuc.edu. Parallel Programming Laboratory ... The clock cycle time is contrained by the longest possible instruction execution ...

| PowerPoint PPT presentation | free to view

Datapaths Lecture L10.2 Sections 10.2, 10.3 ALU (Sect. 7.5 and Lab 6) A modified datapath A datapath with two data registers Switching using a demultiplexer Multiple ...

| PowerPoint PPT presentation | free to view

Think registers as D flip-flops. Each 32-bit register consists of 32 D flip-flips ... data is stored statically as in flip-flops. SRAMs are faster but less ...

| PowerPoint PPT presentation | free to download

Systems I Datapath Design I Topics Sequential instruction execution cycle Instruction mapping to hardware Instruction decoding

| PowerPoint PPT presentation | free to download

DATAPATHS. 1) Registers. a) Parallel Load Register. b) Shift Register. c) Multifunction Register. Register Design Process. Example 4.6. 2) Adders ...

| PowerPoint PPT presentation | free to download

Multicycle Datapath As an added bonus, we can eliminate some of the extra hardware from the single-cycle datapath. We will restrict ourselves to using each functional ...

| PowerPoint PPT presentation | free to download

Title: The Processor: Datapath & Control Subject: Computer Organization & Design Author: Dr. Bassam Kahhaleh Last modified by: Bassam Kahhaleh Created Date

| PowerPoint PPT presentation | free to view

register. written. So, the clock needs to be at least 10 200 50 100 10 = 370ps ... that the register is written and stable only after the next rising edge of ...

| PowerPoint PPT presentation | free to download

... Science Logo Contest $1000 for best logo. Administrative ... Create a single datapath for. lw, sw. beq (j later) add, sub, and, or, slt. Our line of attack ...

| PowerPoint PPT presentation | free to download

Title: Multicycle datapath Subject: CS232 @ UIUC Author: Howard Huang Description 2001-2003 Howard Huang Last modified by: Oskin Mark Created Date

| PowerPoint PPT presentation | free to download

AddressOut and WriteDataOut are output ports. Reset clears regfile and all registers ... Send data to each stage through previous stages ...

| PowerPoint PPT presentation | free to download

CDA 3101 Discussion Section10 Datapath and Control * * Questions 5.3 Describe the effect that a single stuck-at-1 fault (the signal is always 1) would have for the ...

| PowerPoint PPT presentation | free to download

Register File. ALU. Memory. Data In. Address. Data Out. MUX D ... IR: Instruction Register. MicroProgram Counter. Control word. Next MicroInstruction Address ...

| PowerPoint PPT presentation | free to download

Increasing number of transistors, faster computers, and better design tools have ... Remember that there will be a quiz at the beginning of next class. ...

| PowerPoint PPT presentation | free to download

Instruction Decode and ... based on the instruction type are set b/c control logic busy 'decoding' ... during each step of fetch/decode/execute cycles ...

| PowerPoint PPT presentation | free to download

Chapter 5 The Processor: Datapath and Control

| PowerPoint PPT presentation | free to view

Advanced VLSI Design Unit 05: Datapath Units

| PowerPoint PPT presentation | free to view

We need logic to truncate extra 3 bytes data and memory address logic to access ... TRUNCATE LOGIC ... we could use 'LW' and then truncate some bits (24 bits) ...

| PowerPoint PPT presentation | free to download

Pipelining Datapath. Adapted from the lecture notes of Dr. John ... Hardware design. Control Hazard. Decision based on results. Data Hazard. Data Dependency ...

| PowerPoint PPT presentation | free to view

Multiplicand. Multiplier. 1. 0. 0. 0. 1. 0. 0. 1. 1. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 1. 0. 0. 0. 1. 0. 0. 1. 0 ... Flowchart for sequential multiplication ...

| PowerPoint PPT presentation | free to download

Let's take side trip into how these are done at low level. Then come back to look at detailed design of ALU. 6. Looking Inside. Cin also an input ...

| PowerPoint PPT presentation | free to download

SEXT. REG. FILE. SR2 SR1. OUT OUT. MDR. MAR. MEMORY. INPUT. OUTPUT. LD.MDR. MEM.EN, R.W. GateMDR ... SEXT. SEXT. ZEXT. N. Z. P. LOGIC. SEXT. 16. gateMARMUX. IR ...

| PowerPoint PPT presentation | free to view

In this lecture, s from lectures 3, 8 and 9 from the course Computer Architecture ECE 201 by Professor Mike Schulte are used with permission.

| PowerPoint PPT presentation | free to download

http://panda.cs.ndsu.nodak.edu/~achapwes/PICmicro/keyboard/scancodes2.html ... Video (and movies) are a series of stills. If it goes fast enough ...

| PowerPoint PPT presentation | free to view

Embedded Systems in Silicon TD5102 MIPS design Datapath and Control Henk Corporaal http://www.ics.ele.tue.nl/~heco/courses/EmbSystems Technical University Eindhoven

| PowerPoint PPT presentation | free to view

Unclocked vs. Clocked. Clocks used in synchronous logic ... state (value) is based on the clock. Latches: whenever the inputs change, and the clock is asserted ...

| PowerPoint PPT presentation | free to view

Current secure deletion methods do not work. State of the art ... Irrevocably delete corresponding data and file/directory information. Be easy to use ...

| PowerPoint PPT presentation | free to download

Title: CSE 431. Computer Architecture Subject: Lecture 08 Author: Janie Irwin Last modified by: Evgenia Smirni Created Date: 8/19/1997 4:58:46 PM Document ...

| PowerPoint PPT presentation | free to download

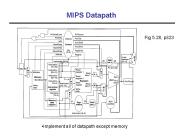

PC. Inst Memory. cmp. mux. Reg File. Reg File. Reg File. Arithmetic & Logical. Load. Store ... PC. Next PC. IR. Inst. Mem. Time. A. B. E. Logical immed ...

| PowerPoint PPT presentation | free to view

Instruction decode and register fetch. Information available: PC, instruction ... type from address. Use polled exceptions. Use Cause register. This is what ...

| PowerPoint PPT presentation | free to download

Algorithm state machine (ASM) charts for FSM ... this is true waits for 8 more BclkX8 star reading the 1st bit waits for 8 more ...

| PowerPoint PPT presentation | free to view

EEL-4713 Computer Architecture Designing a Single Cycle Datapath

| PowerPoint PPT presentation | free to download

Processor fetches an instruction from memory. 5. Control Decodes the Instruction. Processor ... Design of Processor. Analyze the instruction set architecture ...

| PowerPoint PPT presentation | free to download

Title: PowerPoint Presentation Last modified by: Ye Created Date: 1/1/1601 12:00:00 AM Document presentation format: On-screen Show Other titles: Times New Roman ...

| PowerPoint PPT presentation | free to download

... on the instruction, register file input WN is fed by different fields of the instruction ... need an additional multiplexer on WN input. op. rs. rt. offset ...

| PowerPoint PPT presentation | free to view

In a register called program counter (PC) ... Memory, registers, adders, ALU, ... Major time components are ALU, memory read/write, and register read/write. ...

| PowerPoint PPT presentation | free to view

Bus-Based Transfers. How about when there are lots of registers? ... Memory Transfers. Usually one or more buses associated with memory. Address. Data ...

| PowerPoint PPT presentation | free to download

CMOS VLSI Design. Equality Comparator. Check if each bit is equal (XNOR, aka equality gate) ... CMOS VLSI Design. Funnel Shifter. A funnel shifter can do all ...

| PowerPoint PPT presentation | free to download

The control unit is responsible for producing all of the control ... But it requires a little cleverness... Stage 1 involves instruction fetch and PC increment. ...

| PowerPoint PPT presentation | free to view

Real computers have flash memory to boot CPU or go to configuration utility. On (very) old computers had to enter boot program on front panel ...

| PowerPoint PPT presentation | free to download

Advantage: One clock cycle per instruction. Disadvantage: long cycle time ... Clock input (CLK) The CLK input is a factor ONLY during write operation ...

| PowerPoint PPT presentation | free to view

Adapted from the lecture notes of John Kubiatowicz(UCB) and Praveen. The Big Picture: Where are We Now? The Five Classic Components of a Computer ...

| PowerPoint PPT presentation | free to download

Title: Training Last modified by: Alok N Choudhary Created Date: 9/9/1996 11:29:58 AM Document presentation format: On-screen Show Other titles: Times New Roman Arial ...

| PowerPoint PPT presentation | free to download

binary signals that activate the various data ... incrementing the contents of a register ... basic: add, subtract, increment, decrement, & complement ...

| PowerPoint PPT presentation | free to view

Title: CS61C: Machine Structures Author: Dave Patterson Last modified by: Dave Created Date: 8/19/1997 4:58:46 PM Document presentation format: US Letter Paper

| PowerPoint PPT presentation | free to download

http://www.ics.ele.tue.nl/~heco/courses/EmbSystems. Technical University Eindhoven ... HC TD5102. 4. Simplified MIPS implementation to contain only: ...

| PowerPoint PPT presentation | free to download

Chapter Contents 6.1 Basics of the Microarchitecture 6.2 A ... end LOGIC_SPEC; -- Package declaration, in library WORK package LOGIC_GATES is component ...

| PowerPoint PPT presentation | free to download

ECE 4436. ECE 5367. Multi-cycle Datapath. ECE 4436. ECE 5367. Single Cycle Review. S. h. i ... What are some of the main steps in the instruction execution? ...

| PowerPoint PPT presentation | free to view

ELEN 350. Single Cycle Datapath. Adapted from the ... WrEn. 32. Adr. Data. Memory. MemWr. ALU. 32. Mux. W_Src. 3f: The Branch Instruction. beq rs, rt, imm16 ...

| PowerPoint PPT presentation | free to view

Datapath Implementation for Maskless Lithography

| PowerPoint PPT presentation | free to view

Register values read in ID are used in EX and/or MEM stages ... No register is needed after the WB stage, because after WB the instruction is done ...

| PowerPoint PPT presentation | free to view

Unclocked vs. Clocked. Clocks used in synchronous logic ... state (value) is based on the clock. Latches: whenever the inputs change, and the clock is asserted ...

| PowerPoint PPT presentation | free to download

Unclocked vs. Clocked. Clocks used in synchronous logic ... state (value) is based on the clock. Latches: whenever the inputs change, and the clock is asserted ...

| PowerPoint PPT presentation | free to download

Emerging applications have high performance, cost, energy demands ... Applications dominated by tight loops processing large amounts of streaming data. iPhone board ...

| PowerPoint PPT presentation | free to download