MIPS Datapath - PowerPoint PPT Presentation

1 / 6

Title:

MIPS Datapath

Description:

AddressOut and WriteDataOut are output ports. Reset clears regfile and all registers ... Send data to each stage through previous stages ... – PowerPoint PPT presentation

Number of Views:87

Avg rating:3.0/5.0

Title: MIPS Datapath

1

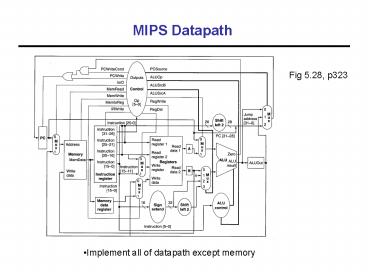

MIPS Datapath

Fig 5.28, p323

- Implement all of datapath except memory

2

System Block Diagram

- MemDataIn is the input port

- AddressOut and WriteDataOut are output ports

- Reset clears regfile and all registers

- Ignore memory control signals for now

3

Implementation/Test Process

- IF, ID, EX, MEM, WB

- Send data to each stage through previous stages

- Directly observe output of a stage to check

results

4

Simulating an Instruction

- Testing is performed by simulating instructions

- Simulate an instruction by

- 1. Applying the correct control sequence

- 2. Applying the instruction to MemDataIn during

the first clock cycle - Testbench needs to apply these signals to the

datapath inputs

5

Control Sequence

- Fig 5.38, p339

- You will change these signals in your testbench

for this lab - Ignore MemRead and MemWrite

6

Testing Stages

IF stage is all logic driving instruction reg and

memory data reg - Memory is external so this

stage is simple - Test this stage by loading the

registers ID stage drives registers A and B -

Test by reading register file (ex. OP x, y,

z) - Initialize register file contents

first EX stage drives ALUOut - Test by

performing OP x, y, z - Initial y, z, check

x MEM stage drives AddressOut, WriteDataOut -

Test with LW, SW, check outputs WB stage drives

register file - Test with LW x, 100(y), check

x