Resumo sobre circuitos l - PowerPoint PPT Presentation

1 / 27

Title:

Resumo sobre circuitos l

Description:

Title: Resumo sobre circuitos l gicos Subject: Fam lias L gicas Author: Nuno Miguel de Figueiredo Garrido Keywords: L gica, Circuitos l gicos, RAM, ROM – PowerPoint PPT presentation

Number of Views:112

Avg rating:3.0/5.0

Title: Resumo sobre circuitos l

1

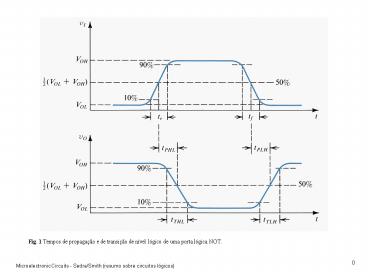

Fig. 1 Tempos de propagação e de transição de

nível lógico de uma porta lógica NOT.

2

Fig. 2 Pontos críticos na característica de

transferência vo(vi) de um inversor genérico.

3

Fig. 3 Tecnologia de fabrico de circuito

integrado e famílias lógicas.

4

Fig. 4 Inversor RTL (Resistor Transistor Logic)

e correspondente característica de transferência

vo(vi) .

5

Fig. 5 Tempo de comutação entre níveis lógicos

num inversor RTL (a). Tensão de entrada (b), e

corrente de colector (c). Na zona toff é retirada

a carga acumulada na junção BE durante a

saturação do TJB, como o transístor está a

comutar para a zona de corte a transição low?high

na saída é lenta (d).

6

Fig. 6 A inserção de um segundo TJB em série no

circuito utilizado para implementar o inversor

permite realizar uma porta lógica NAND dado que

vo A B .

7

Fig. 7 A porta lógica NAND em tecnologia DTL

(Diode Transistor Logic). A tensão VBB é usada

para facilitar a comutação low?high na saída.

8

Fig. 8 O inversor lógico TTL e a sua

característica de transferência vo(vi) .

9

Fig. 9 Tensões e correntes no inversor TTL

quando a entrada é high. Os círculos indicam a

sequência da análise do circuito.

10

Fig. 10 Tensões e correntes no inversor TTL

quando a entrada é low.

11

Fig. 11 A porta lógica NAND realizada em

tecnologia TTL. A utilização de um transístor de

entrada com dois emissores simplifica a

implementação do circuito.

12

Fig. 12 Porta lógica NAND usando transístores e

díodos de Schottky (STTL).

13

Fig. 13 O inversor NMOS com carga (Q2) de

enriquecimento (a) e respectiva característica de

transferência vo(vi) (b).

14

Fig. 14 O circuito inversor NMOS com carga de

depleção (a) e a sua característica de

transferência vo(vi) (b).

15

Fig. 15 O inversor CMOS (a). Característica de

transferência vo(vi) do circuito e zonas de

funcionamento dos transístores QP e QN (b).

16

Fig. 16 Funcionamento equivalente do inversor

CMOS quando a tensão de entrada corresponde ao

nível lógico high e quando a tensão de entrada

corresponde ao nível lógico low. Em cada caso, os

pontos de funcionamento são dados pela

intersecção das características i(v) dos

transístores QP e QN .

17

Fig. 17 (a) O circuito inversor CMOS (b) e o

seu comportamento equivalente.

18

Fig. 18 O comportamento dinâmico de um inversor

CMOS pode aproximar-se por uma carga ou de uma

descarga exponencial (b). A figura (d) mostra a

parte do circuito que está activa durante a

transição high?low, o condensador C representa a

capacidade de entrada da porta lógica seguinte.

19

Fig. 19 A realização de portas lógicas em

tecnologia CMOS obedece a uma regra dual

(complementar), i.e. à inserção de um transístor

NMOS em série corresponde a inserção de um

transístor PMOS em paralelo e vice-versa.

20

Fig. 20 A inserção de vários transístores em

série deve ser compensada pelo aumento, na mesma

proporção, da largura dos transístores para

manter o equilíbrio dos tempo de comutação da

porta lógica.

21

Fig. 21 O interruptor CMOS.

22

Fig. 22 O circuito básico de memória latch e o

seu princípio de funcionamento. O estado actual

depende do estado anterior !

23

Fig. 23 Uma implementação simples de um

flip-flop SR usando dois inversores CMOS e dois

interruptores NMOS.

24

Fig. 24 Utilização de um flip-flop SR na

implementação de uma célula de memória estática

SRAM (Static Random Access Memory).

25

Fig. 25 Implementação de uma célula de memória

dinâmica DRAM (Dynamic Random Access Memory).

26

Fig. 26 Organização física e método de

endereçamento de uma memória RAM de 2MN bits a

partir de uma matriz de 2M linhas e 2N colunas.

27

Fig. 27 Organização de uma memória ROM (Read

Only Memory) de 8 palavras x 4 bits.