Inhoudstafel - PowerPoint PPT Presentation

1 / 113

Title:

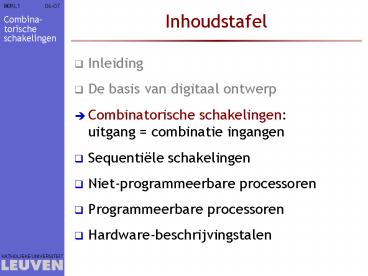

Inhoudstafel

Description:

Title: Combinatorische schakelingen Subject: Digitale Elektronica en Processoren Author: Luc Van Eycken Last modified by: Luc Van Eycken Created Date – PowerPoint PPT presentation

Number of Views:43

Avg rating:3.0/5.0

Title: Inhoudstafel

1

Inhoudstafel

- Inleiding

- De basis van digitaal ontwerp

- Combinatorische schakelingenuitgang

combinatie ingangen - Sequentiële schakelingen

- Niet-programmeerbare processoren

- Programmeerbare processoren

- Hardware-beschrijvingstalen

2

Ontwerp combinatorische schakelingen

Minimalisering Technologie Tijdsgedrag Basisblokke

n RTL

- Minimalisering van Booleaanse functies

- Impact van technologie

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau(ADD, ALU, MUX, )

3

Ontwerp combinatorische schakelingen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Minimalisering van Booleaanse functies

- Karnaugh-kaart

- Minimalisering met Karnaugh-kaarten

- Meerdere uitgangen

- Dont care condities

- Quine-McCluskey

- Impact van technologie

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau(ADD, ALU, MUX, )

4

Waarom minimaliseren?

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Kritisch pad pad met de grootste

vertraging van een ingang naar een uitgang - Bijv. F xyz xyz xy(z z) xy

Kostprijs (11) (44) 3 13 1 3 4

Vertraging 1 2,8 2,4 6,2 1 2,4 3,4

5

Hoe minimaliseren?

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Via manipulatie van Booleaanse uitdrukkingen

- Zeer moeilijk er bestaat geen methode om de

opeenvolgende theoremas te kiezen die leiden tot

de minimale oplossing - Een voorstelling gebruiken waarin opvalt welke

ingang geen belang heeft - Waarheidstabel ?

- Duidelijk dat F 1als x 1 en y

0,onafhankelijk van z - Alleen maar duidelijkvoor z omdat de lijnenvoor

z 0 of 1 ondermekaar liggen - N-kubus of Karnaugh-kaart

x y z F

0 0 0 0 -

0 0 1 0 -

0 1 0 0 -

0 1 1 0 -

1 0 0 1 xyz

1 0 1 1 xyz

1 1 0 0 -

1 1 1 0 -

6

N-kubus

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- n-dimensionale kubus waarbij elke dimensie met 1

variabele overeen komt - 2 variabelen

- 4 variabelen

- 3 variabelen

7

Karnaugh-kaart

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- 2-dimensionale voorstelling van n-kubus

- elk vierkant heeft n buren

- naburige vierkanten hebben slechts voor1

variabele een verschillende waarde

8

Meer dan 4 variabelen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Spiegeling van kaart met 1 variabele minder

- Niet alle buren liggen fysisch naast mekaar!

w

z

zw

00

01

11

10

xy

0

1

3

2

18

19

17

16

00

4

5

7

6

22

23

21

20

01

y

12

13

15

14

30

31

29

28

11

x

8

9

11

10

26

27

25

24

10

01010

00101

9

Meer dan 4 variabelen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Herhaling van kaart met 1 variabele minder

- Onoverzichtelijker naarmate meer variabelen!

v

w

w

z

z

zw

00

01

11

10

00

01

11

10

xy

xy

0

1

3

2

16

17

19

18

00

00

4

5

7

6

20

21

23

22

01

01

y

y

12

13

15

14

28

29

31

30

11

11

x

x

8

9

11

10

24

25

27

26

10

10

10

Invullen Karnaugh-kaart

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Vanuit waarheidstabel of canonische vorm

x y z w F

0 0 0 0 1

0 0 0 1 0

0 0 1 0 0

0 0 1 1 0

0 1 0 0 0

0 1 0 1 1

0 1 1 0 0

0 1 1 1 1

1 0 0 0 1

1 0 0 1 0

1 0 1 0 1

1 0 1 1 0

1 1 0 0 0

1 1 0 1 1

1 1 1 0 0

1 1 1 1 1

0 0 0 0 1

0 0 0 1 0

0 0 1 0 0

0 0 1 1 0

0 1 0 0 0

0 1 0 1 1

0 1 1 0 0

1

0

0

0

0 1 1 1 1

1 0 0 0 1

0

1

0

1

1 0 0 1 0

1 0 1 0 1

1 0 1 1 0

0

1

0

1

1 1 0 0 0

1 1 0 1 1

1

0

1

0

1 1 1 0 0

1 1 1 1 1

11

Gebruiken Karnaugh-kaart

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Zoek zo groot mogelijke subkubussen(

aaneengesloten gebieden met zelfde waarde) - Bijv. F xyzw xyzw xyzw xyzw

xyzw xyzw xyzw

w

z

zw

00

01

11

10

xy

1

0

0

0

00

F

yw

xyw

0

1

1

0

01

yzw

y

0

1

1

0

11

x

1

0

0

1

10

12

Ontwerp combinatorische schakelingen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Minimalisering van Booleaanse functies

- Karnaugh-kaart

- Minimalisering met Karnaugh-kaarten

- Minimale AND-OR realisatie

- Minimale OR-AND realisatie

- Meerdere uitgangen

- Dont care condities

- Quine-McCluskey

- Impact van technologie

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau(ADD, ALU, MUX, )

13

Minimalisering met Karnaugh-kaarten

Waarheidstabel of canonische vorm

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

Maak de Karnaugh-kaart

14

1. Maak de Karnaugh-kaart

F xyz wz xyz wy

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

F xyz

wz

xyz

wy

- Plaats enen op alle plaatsen in de Karnaugh-kaart

waar een productterm 1 is.

15

2. Bepaal alle priemimplicanten

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

wxz

z

y

xyz

1

1

1

wy

1

1

yz

x

1

1

wz

w

1

1

1

wxy

- Analyseer elke 1-minterm

- Bepaal de grootste subkubus(sen) die de minterm

bevat(ten) en voeg ze toe aan de lijst van

priemimplicanten (als ze er nog niet op staan)

16

3. Bepaal alle essentiëlepriemimplicanten

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

wxz

z

y

xyz

1

1

1

wy

essentieel

1

1

yz

x

1

1

wz

essentieel

w

1

1

1

wxy

- Zoek 1-mintermen die slechts in1 priemimplicant

voorkomendit is een essentiële priemimplicant

17

4. Zoek de minimale bedekking

z

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

y

wxz

1

1

1

xyz

1

1

wy

essentieel

x

1

1

yz

w

1

1

1

wz

essentieel

wxy

Fmin xyz wy wz

- Zoek de kleinste set van (zo groot mogelijke)

priemimplicanten die alle 1-mintermen omvat - Initieer de set met de essentiële

priemimplicanten - Voeg telkens een priemimplicant toe die zoveel

mogelijk onbedekte 1-mintermen bevat - Dit is een gulzige (greedy) strategie kies

telkens de beste oplossing zonder rekening te

houden met de gevolgen op toekomstige keuzes - Niet noodzakelijk het globaal optimum

18

Winst t.g.v. minimalisering

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- OrigineelF xyz wy xyz wz

- MinimaalFmin xyz wy wz

w x y z

w x y z

Kostprijs 41 24 23 15

23Vertraging 1 2,8 3,2 7

Kostprijs 41 14 23 14 18 (22

goedkoper)Vertraging 1 2,8 2,8 6,6 (6

sneller)

19

Een tweede voorbeeld

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

v w x y z F

0 0 0 0 0 0

0 0 0 0 1 0

0 0 0 1 0 0

0 0 0 1 1 0

0 0 1 0 0 0

0 0 1 0 1 0

0 0 1 1 0 1

0 0 1 1 1 1

0 1 0 0 0 0

0 1 0 0 1 0

0 1 0 1 0 1

0 1 0 1 1 1

0 1 1 0 0 0

0 1 1 0 1 0

0 1 1 1 0 1

0 1 1 1 1 1

v w x y z F

1 0 0 0 0 0

1 0 0 0 1 0

1 0 0 1 0 0

1 0 0 1 1 0

1 0 1 0 0 0

1 0 1 0 1 1

1 0 1 1 0 0

1 0 1 1 1 1

1 1 0 0 0 0

1 1 0 0 1 1

1 1 0 1 0 0

1 1 0 1 1 1

1 1 1 0 0 0

1 1 1 0 1 1

1 1 1 1 0 0

1 1 1 1 1 1

20

Realisatie als som van 1-mintermen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- F ?(6,7,10,11,14,15,21,23,25,27,29,31)

v

w

x

y

z

Kostprijs 51 126 113 90 Vertraging 1

3,6 6,4 11

21

Maak Karnaugh-kaart

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

v

z

z

y

y

0

0

0

0

0

0

0

0

0

0

1

1

0

1

1

0

x

0

0

1

1

0

1

1

0

w

0

0

1

1

0

1

1

0

22

Bepaal priemimplicanten

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

v

z

z

y

y

1

1

1

1

x

1

1

1

1

w

1

1

1

1

vxyvwy

xyzwyz

vxzvwz

23

Bepaal essentiële priemimplicanten

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

v

z

z

y

y

1

1

1

1

x

1

1

1

1

w

1

1

1

1

Reeds de minimale bedekking

F1min2 vxy vwy vxz vwz

24

Minimale AND-OR realisatie

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- F1min2 vxy vwy vxz vwz

v

w

x

y

z

Kostprijs 11 44 15 22 (76

goedkoper) Vertraging 1 2,8 3,2 7

(34 sneller)

25

Realisatie in meer dan 2 lagen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- F vxy vwy vxz vwz vy(x w) vz(x

w) (x w)(vy vz)

v

w

x

y

z

Kostprijs 11 53 16 (82

goedkoper) Vertraging 1 2,4 2,4 2,4

8,2 (25 sneller)

26

Ontwerp combinatorische schakelingen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Minimalisering van Booleaanse functies

- Karnaugh-kaart

- Minimalisering met Karnaugh-kaarten

- Minimale AND-OR realisatie

- Minimale OR-AND realisatie

- Meerdere uitgangen

- Dont care condities

- Quine-McCluskey

- Impact van technologie

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau(ADD, ALU, MUX, )

27

Duale minimaliseringmet Karnaugh-kaart

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

v

z

z

y

y

0

0

0

0

0

0

0

0

0

0

1

1

0

1

1

0

x

0

0

1

1

0

1

1

0

w

0

0

1

1

0

1

1

0

Realiseer de nullen i.p.v. de enen

28

Bepaal de priemimplicanten

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

v

z

z

y

y

0

0

0

0

0

0

0

0

0

0

0

0

x

0

0

0

0

w

0

0

0

0

vy

vz

(vy)

(vz)

wx

yz

29

Bepaal essentiële priemimplicanten

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

v

z

z

y

y

0

0

0

0

0

0

0

0

0

0

0

0

x

0

0

0

0

w

0

0

0

0

Reeds de minimale bedekking

F0min2 (vy)(wx)(vz)

30

Minimale OR-AND realisatie

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- F0min2 (vy)(wx)(vz)

Kostprijs 11 33 14 14 (84

goedkoper) Vertraging 1 2,4 2,8 6,2 (44

sneller)

31

Samenvatting

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- AND-OR

- OR-AND

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

Realisatie Kost Rel. kost Vertraging Rel. vertraging

Som van 1-mintermen 90 100 11 100

Minimale AND-OR 22 24 7 64

3-lagen 16 18 8,2 75

Minimale OR-AND 14 16 6,2 56

compromis grootte ? snelheid

- Verderop zullen we zien dat er nog andere

mogelijkheden zijn, afhankelijk van de

technologie - OR-AND-INV

- Kostprijs 11 (Rel. kostprijs 12)

- Vertraging 4 (Rel. vertraging 36)

- NOR

- Kostprijs 10 (Rel. kostprijs 11)

- Vertraging 4,2 (Rel. vertraging 38)

32

Ontwerp combinatorische schakelingen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Minimalisering van Booleaanse functies

- Karnaugh-kaart

- Minimalisering met Karnaugh-kaarten

- Meerdere uitgangen

- Dont care condities

- Quine-McCluskey

- Impact van technologie

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau(ADD, ALU, MUX, )

33

Meerdere uitgangen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Nadat alle essentiële priemimplicanten

- gerealiseerd zijn

- Selecteer alle priemimplicanten die de mintermen

realiseren en die al essentieel zijn voor een

andere functie (en dus al gerealiseerd zijn) - yw reeds essentieel voor a en b

- zw reeds essentieel voor a

- Kies de implicant die in het kleinst aantal

functies voorkomt (om de fan-out zo laag mogelijk

te houden) - yw reeds in a en b

- zw reeds in a

c

1

1

1

1

1

y

1

1

1

x

1

1

34

Meerdere uitgangen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Soms voordelig om niet-priemimplicanten te

gebruiken (trial-and-error!) - Mogelijkheden stijgen als meerdere lagen

toegelaten zijn

35

Ontwerp combinatorische schakelingen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Minimalisering van Booleaanse functies

- Karnaugh-kaart

- Minimalisering met Karnaugh-kaarten

- Meerdere uitgangen

- Dont care condities

- Quine-McCluskey

- Impact van technologie

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau(ADD, ALU, MUX, )

36

Dont care condities

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- onvolledig gespecificeerde Booleaanse functie

x y z w a b c d e f g

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

1 1 1 1 1 1 0

BCD ? 7-segment

0 1 1 0 0 0 0

1 1 0 1 1 0 1

a

1 1 1 1 0 0 1

0 1 1 0 0 1 1

b

f

1 0 1 1 0 1 1

g

1 0 1 1 1 1 1

1 1 1 0 0 0 0

c

e

1 1 1 1 1 1 1

1 1 1 1 0 1 1

d

X X X X X X X

X X X X X X X

X X X X X X X

X X X X X X X

X X X X X X X

X X X X X X X

37

1. Maak Karnaugh-kaarten

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

w

w

w

w

z

z

z

z

a

b

c

d

1

0

1

1

1

1

1

1

1

1

1

0

1

0

1

1

0

1

1

1

1

0

1

0

1

1

1

1

0

1

0

1

y

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

x

1

1

X

X

1

1

X

X

1

1

X

X

1

1

X

X

e

f

g

1

0

0

1

1

0

0

0

0

0

1

1

0

0

0

1

1

1

0

1

1

1

0

1

y

X

X

X

X

X

X

X

X

X

X

X

X

x

1

0

X

X

1

1

X

X

1

1

X

X

38

2. Bepaal alle priemimplicanten

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

w

w

w

w

z

z

z

z

a

b

c

d

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

y

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

x

1

1

X

X

1

1

X

X

1

1

X

X

1

1

X

X

e

f

g

1

1

1

1

1

1

1

1

1

1

1

1

y

X

X

X

X

X

X

X

X

X

X

X

X

x

1

X

X

1

1

X

X

1

1

X

X

39

3. Bepaal alle essentiëlepriemimplicanten

a yw z yw x

b y zw zw

c z w y

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

d yw yz yzw zw x

e yw zw

f zw yz yw x

40

4. Zoek de minimale bedekking

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Keuze van de priemimplicant die de

- overblijvende minterm realiseert

- Selecteer alle priemimplicanten die de minterm

realiseren en die al essentieel zijn voor een

andere functie - zw reeds essentieel voor d of e

- yw reeds essentieel voor f

- Kies de implicant die in het kleinst aantal

functies voorkomt - zw reeds in d en e

- yw reeds in f

w

z

g

1

1

1

1

1

y

X

X

X

X

x

1

1

X

X

g yz yz yw x

41

Minimale realisatie

x y z w

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

a

c

b

d

e

f

g

42

Kostprijs vertraging

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Som van 1-mintermen

- Kostprijs 110 (100)

- Inverters 41 4

- AND-poorten 105 50

- OR-poorten 9 9 10 8 5 7 8

56 - Vertraging 1 3,2 5,2 9,4 (100)

- Kritisch pad x?c (9-input OR)

- Minimale 2-lagen-implementatie

- Kostprijs 64 (58)

- Inverters 41 4

- AND-poorten 83 14 28

- OR-poorten 13 24 35 16 32

- Vertraging 1 2,8 3,6 7,4 (79)

- Kritisch pad z?d (3-input AND 5-input OR)

x y y z w a b c d e f g

0 0 0 0 0 1 1 1 1 1 1 0

0 0 0 0 1 0 1 1 0 0 0 0

0 0 0 1 0 1 1 0 1 1 0 1

0 0 0 1 1 1 1 1 1 0 0 1

0 0 1 0 0 0 1 1 0 0 1 1

0 0 1 0 1 1 0 1 1 0 1 1

0 0 1 1 0 1 0 1 1 1 1 1

0 0 1 1 1 1 1 1 0 0 0 0

1 1 0 0 0 1 1 1 1 1 1 1

1 1 0 0 1 1 1 1 1 0 1 1

43

Ontwerp combinatorische schakelingen

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Minimalisering van Booleaanse functies

- Karnaugh-kaart

- Minimalisering met Karnaugh-kaarten

- Meerdere uitgangen

- Dont care condities

- Quine-McCluskey

- Impact van technologie

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau(ADD, ALU, MUX, )

44

Quine-McCluskey

- Minimalisering

- Karnaugh-kaart

- Minimalisering

- Multi-uitgang

- Don't care

- Quine-McClusky

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Karnaugh-kaart

- handmatige methodevisuele patroonherkenning

- geen garantie op de optimale oplossing (gulzige

strategie) - Quine-McCluskey

- computermethode,gebruik makend van tabellen

- optimale oplossing

- vormt de basis van alle CAD-software van het

ontwerpen van schakelingen - moeilijk met de hand ? zie boek

45

Ontwerp combinatorische schakelingen

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- Minimalisering van Booleaanse functies

- Impact van technologie

- Gate array NAND, NOR

- Componentenbibliotheek AOI, OAI,

- FPGA

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau(ADD, ALU, MUX, )

46

Gate array

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- Aanpassing nodig omdat ze enkel m-input NAND- of

m-input NOR-poorten bevatten - INV-AND-OR (minimalisering 1-mintermen)? m-input

NAND - INV-OR-AND (minimalisering 0-maxtermen)? m-input

NOR - Aanpassing aan de technologie

47

Decompositie

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

a b c d (a b) (c d) ((a b)

c) d

48

Conversie optimalisering

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- Conversie gebaseerd op dewetten van De Morgan

- Optimalisering

(xy) x y

(x y) xy

49

Enkele voorbeelden

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

50

Realisatie van een inverter

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

Nadeel verdubbeling belasting van de sturende

poort

Nadeel langere bedrading

51

Optimalisering vertraging (retiming)

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- tracht alle vertragingen van een ingangnaar een

uitgang gelijk te maken - Bijv. realiseer onderstaand voorbeeld enkel met

3-input NAND-poorten en optimaliseer de vertraging

52

Voorbeeld optimalisering vertraging

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- 1e ontbinding in3-input NAND

- 2e ontbinding in3-input NAND

Vertraging 61,8 10,8

Vertraging 41,8 7,2 (67)

53

Ontwerp combinatorische schakelingen

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- Minimalisering van Booleaanse functies

- Impact van technologie

- Gate array

- Componentenbibliotheek AOI, OAI,

- FPGA

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau(ADD, ALU, MUX, )

54

Bibliotheek van componenten

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- ASICs hebben AOI en OAI klein en snel!

- Voor kleine functies realiseer de inverse

functie met AND-OR of OR-AND - Bijv. 2e voorbeeld minimaliseringF

?(6,7,10,11,14,15,21,23,25,27,29,31) - Realisatie als som van 1-mintermen

- kostprijs 90

- vertraging 11

- Minimale realisatie als OR-AND

- kostprijs 14 (16)

- vertraging 6,2 (56)

55

Voorbeeld kleine functie

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- F ?(6,7,10,11,14,15,21,23,25,27,29,31) ?F

?(0,1,2,3,4,5,8,9,12,13,16,17,18,19,20,

22,24,26,28,30)

Kostprijs 51 6 11 (12) Vertraging 1 3

4 (36)

56

Grote functies (meerlagen realisatie)

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

Realiseer als AND-OR of OR-AND

Transformeer naar NAND of NOR

Bepaal kritisch pad

Vervang zoveel mogelijk 2 lagen poortenop het

kritisch pad door AOI/OAI (lagere kost / geen

slechtere vertraging)

Vervang zoveel mogelijk 2 lagen poortenbuiten

het kritisch pad door AOI/OAI (lagere kost)

57

Voorbeeld F wz z(wy)

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- Realiseer met AND en OR

Kostprijs 14 Vertraging 7,2

- Transformeer naar NAND en NOR

Kostprijs 11 (79) Vertraging 5,2 (72)

- Bepaal het kritisch pad

58

AOI/OAI gebruiken (1e poging)

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- Vervang 2 poorten op kritisch paddoor AOI

Kostprijs 10 (71) Vertraging 5,6 (78)

Kostprijs 10 (71) Vertraging 5,6 (78)

- Vervang 2 poorten buiten kritisch paddoor een

component uit de bibliotheek

59

AOI/OAI gebruiken (2e poging)

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- Vervang 2 poorten op kritisch paddoor OAI

Kostprijs 10 (71) Vertraging 5,6 (78)

Kostprijs 7 (50) Vertraging 3,6 (50)

- Vervang 2 poorten buiten kritisch paddoor een

component uit de bibliotheek

60

AOI/OAI gebruiken (3e poging)

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- Vervang 2 poorten op kritisch paddoor OAI

Kostprijs 10 (71) Vertraging 3,8 (53)

- Analyseer het nieuwe kritische pad

Kostprijs 9 (64) Vertraging 3,8 (53)

61

Ontwerp combinatorische schakelingen

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- Minimalisering van Booleaanse functies

- Impact van technologie

- Gate array

- Componentenbibliotheek

- FPGA

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau(ADD, ALU, MUX, )

62

Aanpassing aan FPGA

- Minimalisering

- Technologie

- Gate array

- Chip-ontwerp

- FPGA

- Tijdsgedrag

- Basisblokken RTL

- CLB

- 2 functies van 4 variabelen

- 1 functie van 5 variabelen

- Aanpassing analoog aan vorige methode, maar zoek

naar subschakelingen van 4 of 5 variabelen i.p.v.

AOI/OAI - Voor FPGAs (of ASICs) gebeurt de aanpassing

voor - prototype software (automatisch)

- eindproduct handmatige optimalisering

kan voordelig zijn

63

Ontwerp combinatorische schakelingen

- Minimalisering

- Technologie

- Tijdsgedrag

- Hazard

- Basisblokken RTL

- Minimalisering van Booleaanse functies

- Impact van technologie

- Tijdsgedrag

- Hazards vermijden

- Basisbouwblokken op RTL-niveau(ADD, ALU, MUX, )

64

Hazard

- Minimalisering

- Technologie

- Tijdsgedrag

- Hazard

- Basisblokken RTL

- bijkomende niveauverstoring (glitch) t.g.v.

tijdsgedrag - Statische hazardconstant niveau vertoont

verstoring - statische 1-hazarduitgang moet 1 blijven maar

wordt even 0 - statische 0-hazarduitgang moet 0 blijven maar

wordt even 1 - Dynamische hazarduitgang schakelt niet

eenmaal(bijv. 1 ? 0) maar meerdere malen(bijv.

1 ? 0 ? 1 ? 0)

65

Voorbeeld statische hazard

z

y

- Minimalisering

- Technologie

- Tijdsgedrag

- Hazard

- Basisblokken RTL

1

1

1

1

x

Statische 1-hazard

66

Voorbeeld dynamische hazard

- Minimalisering

- Technologie

- Tijdsgedrag

- Hazard

- Basisblokken RTL

67

Hazards vermijden

- Minimalisering

- Technologie

- Tijdsgedrag

- Hazard

- Basisblokken RTL

- Oorzaak

- Verschil in vertraging van eenzelfde ingang naar

eenzelfde uitgang langs verschillende paden - Oplossing

- Voeg redundante termen toe om disjuncte gebieden

in de Karnaugh-kaart te bedekken - 1-hazardsmintermen voor disjuncte 1-gebieden

- 0-hazardsmaxtermen voor disjuncte 0-gebieden

68

Hazards vermijden

z

y

- Minimalisering

- Technologie

- Tijdsgedrag

- Hazard

- Basisblokken RTL

1

1

1

1

x

69

Hazard-problemen

- Minimalisering

- Technologie

- Tijdsgedrag

- Hazard

- Basisblokken RTL

- Hazards zijn moeilijk handmatig te detecteren ?

simulatie tijdsgedrag belangrijk - De kans op hazards vergroot naarmate tPLH en tPHL

meer verschillen - Wanneer zijn hazards een probleem?

- Als signaalovergangen gebruikt worden (bijv.

klok) - Als signaalniveaus gebruikt worden en de hazard

komt op een slecht ogenblik (cfr. sequentiële

schakelingen) - Samen met de klok van een synchrone schakeling

- Gelijk wanneer in een asynchrone schakeling

70

Ontwerp combinatorische schakelingen

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- Minimalisering van Booleaanse functies

- Impact van technologie

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau

- Optellen aftrekken

- Vermenigvuldigen

- (A)LU

- (De)multiplexer

- Prioriteitsencoder

- Vergelijken

- Schuifoperaties

71

Interludium XOR-poort

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- Herkenbaar aan dambordpatroon

- Realiseerbaar als boom van 2-input XORs

- Bruikbaar als programmeerbare inverter

x ? y ? z ? w

x ? y ? z

x ? y ? z ? w (x ? y) ? (z ? w)

72

Halve opteller (Half Adder)

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

xi yi ci1 si

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

xi

yi

HA

ci1

1 CLB

si

73

Opteller (Full Adder)

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

xi yi ci ci1 si

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 0 1 1 0

1 1 1 1 1

xi

yi

FA

ci1

ci

si

1 CLB

74

Alternatieve implementatie

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

xi yi ci ci1 si

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 0 1 1 0

1 1 1 1 1

xi

yi

FA

ci1

ci

si

1 poort minder,grotere vertraging van xi yi

naar ci1,dezelfde vertraging van ci naar ci1

75

Ripple-carry opteller

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- 4-bit ripple-carry opteller

x0

y0

x1

y1

x2

y2

x3

y3

FA

c00

c1

FA

c2

FA

c3

FA

c4

s0

s1

s2

s3

Kritisch pad x0 of y0 ? cn 1 XOR n AND n

OR Vertraging 3,2 n ? 2,4 n ? 2,4

76

Carry-look-ahead opteller

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- Ripple-carry opteller is traag omdat het kritisch

pad van x0 naar cn1 lang is - Versnelling mogelijk door cn1 rechtstreeks

(bijv. in 2 lagen) te berekenen uit c0, x0xn en

y0yn carry-look-ahead - Cascadeerbare oplossingmet carry-generate

gien carry-propagate pi - ci1 gi pi ci

- gi xi yi

- pi xi yi xiyi

- Opmerking ci1 hangt nietrechtstreeks af van

xi of yi

77

Carry-look-ahead opteller

xi

yi

si

xin-1

yin-1

sin-1

xi2

yi2

si2

xi1

yi1

si1

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

x

y

x

y

x

y

x

y

c

s

c

s

c

s

c

s

g

p

g

p

g

p

g

p

g0

p0

gn-1

pn-1

g2

p2

g1

p1

CLA generator

g(i,in-1)

g(0,n-1)

ci

c0

p(0,n-1)

p(i,in-1)

c1

c3

c2

cn

cin

ci1

ci3

ci2

- CLA generatorfuncties

78

Carry-look-ahead opteller

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- Realisatie van CLA-functies in 2 lagen

- Kritisch pad xi of yi ? cin1 XOR 1 n-input

AND 1 n-input OR - Vertraging 3,2 2?(1,6 n?0,4) 6,4 0,8n

- Cascade van k-bit CLA-generatorsin ?logk n?

niveaus bijv. n 24, k 4 - Vertraging 3,2 (2?logk n? - 1)?(3,2 0,8k)?

logaritmisch stijgend

79

Opteller-aftrekker (adder-subtractor)

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

S Functie Bewerking

0 X Y Optelling

1 X - Y X Y X Y 1 Aftrekking

Alleen voor 2-complement!

80

Ontwerp combinatorische schakelingen

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- Minimalisering van Booleaanse functies

- Impact van technologie

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau

- Optellen aftrekken

- Vermenigvuldigen

- (A)LU

- (De)multiplexer

- Prioriteitsencoder

- Vergelijken

- Schuifoperaties

81

Parallelle vermenigvuldiger

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- 1-bit 1-bit vermenigvuldiger

- 2-bit 2-bit vermenigvuldiger

AND-poort

b0 a0 c0 a0 b0

0 0 0

0 1 0

1 0 0

1 1 1

a0b0

a0b1

a1b0

a1b1

Elke term is 11-vermenigvuldiger

82

4-bit 3-bit vermenigvuldiger

b0

a0

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

b1

b2

b3

b0

a1

b1

b2

b3

0

4-bit opteller

s0

s1

s2

s3

cout

b0

a2

b1

b2

b3

4-bit opteller

s0

s1

s2

s3

cout

c0

c1

c2

c3

c4

c5

c6

Kostprijs O(nm)

83

2-complement vermenigvuldiger

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- Hou rekening met de tekenbit

- Bijv. 11112 11112 000000012

- ( 11112 -110 -8 4 2 1 )

- Converteer naar sign-magnitude-voorstelling ?

dikwijls minder hardware

1 -1 ? 11111111

2 -1 ? 11111110

4 -1 ? 11111100

-8 -1 ? 00001000

-1 -1 ? 00000001

84

Ontwerp combinatorische schakelingen

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- Minimalisering van Booleaanse functies

- Impact van technologie

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau

- Optellen aftrekken

- Vermenigvuldigen

- (A)LU (Aritmetische ) logische eenheid

- (De)multiplexer

- Prioriteitsencoder

- Vergelijken

- Schuifoperaties

85

Logische eenheid

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- component die alle 16 Booleaanse functies van 2

bits kan realiseren - Eenheid voor n bits n eenheden voor 1 bit

- 4 bits S3S2S1S0 die de functie selecteren

- Codering van de selectiebits is identiek aan het

functienummer in de tabel van de mogelijke

Booleaanse functies

86

Functies logische eenheid

Functiewaarden voor x,y Functiewaarden voor x,y Functiewaarden voor x,y Functiewaarden voor x,y

1-mintermen 00 01 10 11 Uitdrukking

0 0 0 0 F0 0

m3 0 0 0 1 F1 xy

m2 0 0 1 0 F2 xy

m2 m3 0 0 1 1 F3 x

m1 0 1 0 0 F4 xy

m1 m3 0 1 0 1 F5 y

m1 m2 0 1 1 0 F6 xy xy

m1 m2 m3 0 1 1 1 F7 x y

m0 1 0 0 0 F8 (x y)

m0 m3 1 0 0 1 F9 xy xy

m0 m2 1 0 1 0 F10 y

m0 m2 m3 1 0 1 1 F11 x y

m0 m1 1 1 0 0 F12 x

m0 m1 m3 1 1 0 1 F13 x y

m0 m1 m2 1 1 1 0 F14 (xy)

m0 m1 m2 m3 1 1 1 1 F15 1

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

87

Implementatie logische eenheid

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

xi

yi

S0

S1

S2

xi

yi

S3

LU

S0..3

fi

fi

88

Arithmetic-Logic Unit

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- component die de volgende functies realiseert

- 4 aritmetische bewerkingen optelling,

aftrekking, increment (1), decrement (-1) - 4 logische bewerkingen AND, OR, INV, identiteit

(doorgeven, nul-operatie) - Realisatie

- Opteller voor aritmetische operaties

- Arithmetic-Logic Extender ervoor

- conditionering ingangen opteller(cfr. XOR bij

aftrekking) - logische operaties

89

Implementatie ALU

a0

b0

a1

b1

a2

b2

a3

b3

a4

b4

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

S01

M

ALE

ALE

ALE

ALE

ALE

X

Y

cout

FA

FA

FA

FA

FA

f0

f1

f2

f3

f4

overflow

M kiest het type bewerking 0 logisch, 1

aritmetisch S0 en S1 kiezen de bewerking

90

ALU-functies

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

M S1 S0 Functie F X Y C0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Complement A A 0 0

AND A AND B A AND B 0 0

Identity A A 0 0

OR A OR B A OR B 0 0

Decrement A-1 A all 1 0

Add AB A B 0

Subtract A-B A B 1

Increment A1 A all 0 1

91

Generatie carry-in

M S1 S0 Functie F X Y C0

0 0 0 Complement A A 0 0

0 0 1 AND A AND B A AND B 0 0

0 1 0 Identity A A 0 0

0 1 1 OR A OR B A OR B 0 0

1 0 0 Decrement A-1 A all 1 0

1 0 1 Add AB A B 0

1 1 0 Subtract A-B A B 1

1 1 1 Increment A1 A all 0 1

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

92

ALE-implementatie X

M S1 S0 Functie F X Y C0

0 0 0 Complement A A 0 0

0 0 1 AND A AND B A AND B 0 0

0 1 0 Identity A A 0 0

0 1 1 OR A OR B A OR B 0 0

1 0 0 Decrement A-1 A all 1 0

1 0 1 Add AB A B 0

1 1 0 Subtract A-B A B 1

1 1 1 Increment A1 A all 0 1

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

M

S0

S0

X

S1

S1

1

1

1

bi

1

1

1

1

1

1

1

ai

1

1

1

1

1

1

93

ALE-implementatie Y

M S1 S0 Function F X Y C0

0 0 0 Complement A A 0 0

0 0 1 AND A AND B A AND B 0 0

0 1 0 Identity A A 0 0

0 1 1 OR A OR B A OR B 0 0

1 0 0 Decrement A-1 A all 1 0

1 0 1 Add AB A B 0

1 1 0 Subtract A-B A B 1

1 1 1 Increment A1 A all 0 1

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

M

S0

S0

Y

S1

S1

1

1

1

1

bi

1

1

ai

1

1

94

Ontwerp combinatorische schakelingen

- Minimalisering

- Technologie

- Tijdsgedrag

- Basisblokken RTL

- Opteller

- Vermenig-vuldiger

- ALU

- (De)Mux

- Prioriteits-encoder

- Comparator

- Schuiver

- Minimalisering van Booleaanse functies

- Impact van technologie

- Tijdsgedrag

- Basisbouwblokken op RTL-niveau

- Optellen aftrekken

- Vermenigvuldigen

- (A)LU (Aritmetische ) logische eenheid

- (De)multiplexer

- Prioriteitsencoder