Sin ttulo de diapositiva - PowerPoint PPT Presentation

1 / 8

Title:

Sin ttulo de diapositiva

Description:

HDL Desenvolupat per TI, Intermetrics, IBM (1985) ... Noms v lids : Noms inv lids: A last_at_value. X0 5bit_counter. counter _A0. Next_value A0_ ... – PowerPoint PPT presentation

Number of Views:44

Avg rating:3.0/5.0

Title: Sin ttulo de diapositiva

1

Sistemes Digitals (I)

2_VHDL_1 - 1

Introducció

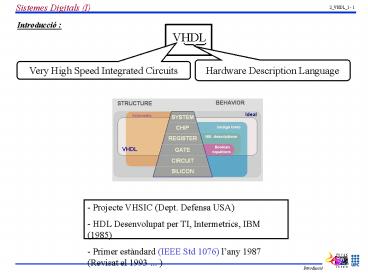

VHDL

Hardware Description Language

Very High Speed Integrated Circuits

- Projecte VHSIC (Dept. Defensa USA) - HDL

Desenvolupat per TI, Intermetrics, IBM (1985) -

Primer estàndard (IEEE Std 1076) lany 1987

(Revisat el 1993 ... )

Introducció

2

Sistemes Digitals (I)

2_VHDL_1 - 2

Estructura dun programa en VHDL

LIBRARY ieee USE ieee.std_logic_1164.all ENTITY

logica IS PORT ( a,b,c IN

STD_LOGIC s OUT

STD_LOGIC) END logica ARCHITECTURE

prova OF logica IS SIGNAL punt_mig

STD_LOGIC BEGIN END

prova

(Estructura simple per al disseny digital)

- Llibreries ieee.std_logic_1164

- ieee.std_logic_arith

- ieee.std_logic_unsigned

- Tipus dentrades / sortides IN, OUT, INOUT

- Tipus de senyals STD_LOGIC

- STD_LOGIC_VECTOR(7 DOWNTO 0)

- INTEGER RANGE 0 TO 255

PROCESS (a,b) BEGIN punt_mig

lt a AND b END PROCESS

PROCESS (punt_mig,c) BEGIN s

lt punt_mig OR c END PROCESS

Definició dels blocs lògics bàsics en VHDL

3

Sistemes Digitals (I)

2_VHDL_1 - 3

Identificadors i paraules reservades

Identificadors

- Els identificadors són utilitzats per a posar

nom als diferents elements del disseny. - Les

limitacions són les següents - Caràcters

alfabètics de A .. Z i de a .. z

- Caràcters

numèrics 0 .. 9

- Caràcter _ (Underline) - El

nom sha diniciar amb un caràcter alfabètic. -

El nom no pot finalitzar amb un caràcter _ ni

tenir-ne dos de consecutius. Noms vàlids

Noms invàlids A last_at_value X0 5bit_co

unter counter _A0 Next_value A0_ generate

_read_cycle clock__pulse

Definició dels blocs lògics bàsics en VHDL

4

Sistemes Digitals (I)

2_VHDL_1 - 4

Paraules reservades

abs entity next select access exit nor sever

ity after file not signal alias for null sha

red all function of sla and generate on sll

architecture generic open sra array group or

srl assert guarded others subtype attribute i

f out then begin impure package to block in

port transport body inertial postponed type b

uffer inout procedure unaffected bus is proce

ss units case label pure until component libr

ary range use configuration linkage record va

riable constant literal register wait disconnec

t loop reject when downto map rem while else

mod report with elsif nand return xnor end

new rol / ror

Definició dels blocs lògics bàsics en VHDL

5

Sistemes Digitals (I)

2_VHDL_1 - 5

Símbols i dades

Exemples

Nombres

- Enters

23 46E5

B11000110 b1111_0101_1010 XC6 XF5A

- Cadenes binàries - Cadenes hexadecimals

Lletres

- Caràcters - Cadenes de caràcters - Concatenació

A z Una paraula Pot incloure de

tot ?çÇ_at_... Concatena

00011010

Constants

CONSTANT nombre_de_bits INTEGER 4 CONSTANT

adreca str_logic_vector(7 down to 0)

XA4 GENERIC (nombre_bits integer 8)

Dins Entity !!!

- Enteres

- binàries hexa.

- - generic

Senyals

SIGNAL suma1,suma2 INTEGER RANGE 0 TO 255

suma1 lt suma2 1 SIGNAL bit1

STD_LOGIC bit lt 1 SIGNAL

vector STD_LOGIC_VECTOR (7 DOWNTO 0)

vector lt XA4

- Enteres

- Std_logic

- Std_logic_vector

Definició dels blocs lògics bàsics en VHDL

6

Sistemes Digitals (I)

2_VHDL_1 - 6

Declaració de tipus descalars

TYPE estat IS RANGE (parat, primer,

segon) SIGNAL quin_estat, nou_estat

estat BEGIN quin_estat lt nou_estat

quin_estat lt parat

- Definicions molt potents. - Detectar errades en

lassignació de valors. - Detectar senyals

del mateix tipus.

Funcions per a operacions aritmètiques i lògiques

Dada 1

Dada 2

Operador

Descripció

Resultat

Vector Enter Vector Vector Enter Vector Vector Ent

er Vector

Desplaçament (shift) lògic Desplaçament (shift)

aritmètic Rotació

sll,srl sla,sra rol,ror

B10001010 srl 3 gt B00010001 B01011001

sll 3 gtB11001000 B10001010 sra 3 gt

B11110001 B01011001 sla 3 gtB11001111

Qualsev. tip. Dada1 Booleà Qualsev.

tip. Dada1 Booleà

Comparador igual / diferent Comparadors gran /

petit

, / lt, lt, gt , gt

and,or,nand nor,xor,xnor

Bit,Vector Dada1 Dada1

Funcions lògiques.

Definició dels blocs lògics bàsics en VHDL

7

Sistemes Digitals (I)

2_VHDL_1 - 7

Estructures condicionals

Sentència if

LATCH!!!

if ck1 then Q lt D end if

if expressió_booleana then

estructura_seqüencial elsif

expressió_booleana then

estructura_seqüencial else

estructura_seqüencial

end if

if sel0 then sortida lt entrada_0

else sortida lt entrada_1 end if

if a /b then sortida lt 1 else

sortida lt 0 end if

Sentència case

case sel is when 00 gt y lta when

01 gt y ltb when 10 gt y ltc

when others gt y ltd end case

case expressió_booleana is when

selecció_1 gt estructura_seqüencial_1

when selecció_2 gt estructura_seqüencial_2

....... when others gt

estructura_seqüencial_n end case

Definició dels blocs lògics bàsics en VHDL

8

Sistemes Digitals (I)

2_VHDL_1 - 8

Sentència loop

loop estructura_seqüencial (if

condició then exit end if ) (exit when

condició) (next when condició)

end loop

?

volta lt 0 loop exit when volta16

vector(volta1)lt vector(volta) voltaltvolta1

end loop

volta lt 0 while voltalt16 loop volta lt volta

1 vec2(volta) lt vec1(volta) end loop

Sentència while loop

while expressió_booleana loop

estructura_seqüencial end loop

?

downto

a10 for a in 0 to 7 loop b a end

loop

Sentència for loop

?

for constant_no_declarada in valor_discret

loop estructura_seqüencial end

loop

a10 i b7

Definició dels blocs lògics bàsics en VHDL