Prsentation PowerPoint - PowerPoint PPT Presentation

1 / 18

Title:

Prsentation PowerPoint

Description:

Susanta K Pal. PMD Collaboration Meeting , December 26th 2005. 4. 3 boards compose the set ... Susanta K Pal. PMD Collaboration Meeting , December 26th 2005. 11 ... – PowerPoint PPT presentation

Number of Views:38

Avg rating:3.0/5.0

Title: Prsentation PowerPoint

1

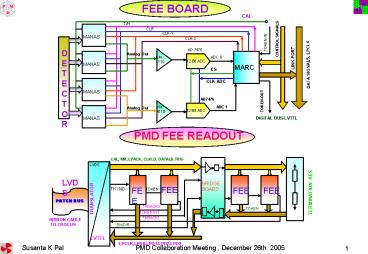

FEE BOARD

CAL

T/H

CLR

CLK-1

MANAS

CLK-2

CONTROL SIGNALS

TOKEN-IN

D ETECTOR

AD 7476

Analog Out

LINK PORT

ADC 0

KM 4110

12 Bit ADC

DATA SIGNALS, LPCLK

MANAS

MARC

CS

CLK-ADC

MANAS

TOKEN-OUT

AD7476

ADC 1

KM 4110

Analog Out

12 Bit ADC

MANAS

DIGITAL BUS-LVTTL

PMD FEE READOUT

CAL, MR, LPACK, CLKLD, DATALD,TRIG

LVDS

FEE

FEE

LVDS

BRIDGE BOARD

FEE

FEE

TK IN0

TERMINATION RES

TOKEN

TRANSLATOR

PATCH BUS

TKBACK0

TOKEN

TOKEN IN1

TKBACK1

RIBBON CABLE TO CROCUS

EN/DIR

LVTTL

LPCLK,LPD0.LPD1,LPD2,LPD3

2

DISPATCHING

VME TRIGGER DISPATCHING

LTU

CTP

TRIGGER

L0

BUSY

PRE PULSE

40 meters LVDS LINKPORTS TRIGGER BUSY, prepulse

and L0

CROCUS CRATE

3

READ OUT

- The Cluster Read Out Concentrator Unit System

(CROCUS) - The VME Trigger Dispatching Crate

- The Cluster Read Out Concentrator Unit System

(CROCUS) has the following features - Gather and Concentrate the information coded on

the FEE - Pass the data to DAQ

- Drive the FEEs via PATCH bus Controllers

- Receive and distribute the trigger signals ( L0,

L1, SYNC ) - Allow the calibration of the Detector

- Detect the breakdown on the data acquisition chain

4

READ OUT

- 3 boards compose the set CROCUS

- The board CROCUS_BACK which is the back plane of

the crate - The board CROCUS_FRT which are connected to the

chamber FEE - The board CROCUS_CRT which concentrates the data

of board CROCUS_FRT to the acquisition

- CROCUS_BACK

- The back plane do

- The distribution of boards supply

- The interconnection of the buses of datum

linkport between the CROCUS_CRT and the

CROCUS_FRT - The distribution of the serial links from

CROCUS_CRT to CROCUS_FRT - The distribution of the signals L0, L1A, L1R,

SYNC from CROCUS_CRT to the CROCUS_FRT - The concentration of the BUSY signals to

CROCUS_CRT - The distribution of the control signals of

CROCUS_FRT boards ( RESET, FLAG, TIMEXP )

5

READ OUT

CROCUS_FRT

- The objective of this board

- The management of FEEs via Control PATCH bus

- The Level-I data concentration which is coming

from FEEs - The transfer of the data to Level-II data

concentration crocus system - The sending of calibration signal to Detectors

CROCUS_CRT

The objective of this board

- The data acquisition from the frontal boards (

upto 5 boards equal to 10 linkports ) - The distribution of trigger signals L0, L1R, L1A,

SYNC to the frontal boards - The drive and boot of the frontal boards

- The concentration of the data to the acquisition

system via SIU boards - The management of the frontal boards BUSY signals

- The management of Level-I breakdown

- The sending of the test and debug software from

the VMETCI crate on LVDS

6

CROCUS Structure

TO 10 PATCH BUS

J T A G

J T A G

J T A G

J T A G

J T A G

J T A G

J T A G

J T A G

J T A G

J T A G

Front board

Front board

Front board

Front board

Front board

Front board UP TO 10 PATCH connected via

linkport and serial port 2 DSP analog

Devices From 1 to 5 front boards

Dsp Analog Device 21160 BGA 400 Pins at 80Mhz

J T A G

J T A G

Concentrator board

EEPROM

- 2 DSP analog Devices witch are driving the front

board

FPGA SIU Interface

SIU INTERFACE BOARD

Debug

- 2 DSP for the event building, the monitoring, the

debug.

TO VME DISPATCHING

FPGA TRIGGER

Trigger config

- 1 FPGA for the trigger and board control

- 1 FPGA to make the interface with the SIU

DDL to RORC

- 1 SIU interface board

7

CROCUS Structure

FRONT BOARD

FRONT BOARD

FRONT BOARD

DSP FRT CONTROL PATCH

DSP FRT CONTROL PATCH

DSP FRT CONTROL PATCH

4

Rx

Rx

Rx

4

4

Sport

Sport

CONCENTRATOR BOARD

Lps

Lps

DSP CRT FRONT C

Tx

DSP CRT FRONT B

Tx

Rx/Tx

Rx/Tx

Lp 4

Resets, Boots, Flags, L0 L1accept, L1reject,

Busys, Sync

Lp 4

Boot Eprom

Data

Lp Config

To VME Dispatching Crate

L0

LCA TRIGGER CONFIG

LVDS

DSP DEBUG

Link-ports debug

DSP CRT A

4

To VME Dispatching Crate

Sync Test

Flags

Busy

Irqs

Lp 4

Trigger config

Lp Trigger

Lp

LCA SIU

Lp Boot

Lp Config

Linkport

Lp Data rescue mode

Flags

Bus config

Sport

// Bus

Control bus

Configuration bus

SIU INTERFACE

To RORC

8

CROCUS Rates

1,2µs L0

20MB/s

5,2µs L1

DSP F1

DSP F2

DSP F3

DSP F4

DSP F5

DSP F6

DSP F7

DSP F8

DSP F9

DSP F10

67,8 µs

Lport 8 bits 40MHz

88µs L2

5136 words

40MB/s

DSP Concentrator first A

DSP Concentrator_C ( 5680 words)

DSP Concentrator_B ( 5680 words)

68µs

135,8 µs

Parallel Bus 64 bits 40MHz 320MB/s

SIU Interface

6800 words

100MB/s

272 µs

407,8 µs

RORC

9

READ-OUT

L2 ( 88 ?s )

67,8 ?s

38 ?s

L0 ( 1,2 ?s )

135,8 ?s

407,8 ?s

T0

L1 ( 5,2 ?s )

Bus PATCH Transfert

Event 1 building level I

Coding

Event 1 building level II

DSP concentrator Transfert

Event 1 building level III

DDL Transfert

Bus PATCH Transfert

Event 2 building level I

Coding

Event 2 building level II

DSP concentrator Transfert

BUSY

10

READ OUT

- T1.2 us

- L0 reaches PMD FEE and CROCUS

- CROCUS Switches to BUSY

- 38 us is necessary for 64 Channels encoding

(600ns/channel) - T7.4 us

- If L1 Reject, CROCUS is ready for new Events

- T 88 us

- L2 arrives

- If reject L2 event building is cancelled

otherwise proceeds. - The total BUSY time may be permitted upto 88 or

100 us (approximately). - Signal shaping, encoding, pedestal subarction and

store data in MARC 40 us. - The time left for patch bus transmission 60 us.

- No. of 32 bit words _at_40Mhz( DSP link speed, in

nibble transmission) can be - transferred in 60 us (4060)/(24) 300

Words. one byte 2 nibbles, 32 bit 4 bytes

11

Timing of the acquisition Sequence

12

DAQ-ARCHITECTURE

13

Event Logic Structure

14

DATE Headers

15

Common Data Header

The Common Data Header (CDH) needs to be

generated by the detector electronics together

with the Trigger System and transmitted over the

DDL (first 8 bytes of each fragment).

31

24

16

8

0

Block Length

0

Bunch Crossing

0

L1 Trigger Message

Version

1

Mandatory Optional Must be Zero

0

2

Orbit Number

3

Block Attributes

Participating Sub-Detectors

4

0

Mini Event ID

StatusError Bits

5

Trigger Classes Low

6

ROI Low

0

Trigger Classes High

ROI High

7

16

Streamlined Event Format

GDC with 2 LDCs

Only 1 LDC

LDC

sub-event header

(header extension)

LDC

Contiguous in virtual memory

17

Paged Event Format

bank0

vector for header

vector 2

base event header

Number of vectors

header extension

vector 1

vector 3

equipment header 1

equipment header 2

equipment header 3

bank1

bank2

data 1a

data 1b

data 2

data 3

vector 1a

vector 1b

18

DISPATCHING

VME bus

Bus Interface

DSP

Debug Trigger Interface

F F T

CPU MASTER BOARD

TTCRX

Trigger Control

TRIGGER from TTCEX

L0

BUSY

Pre PULSE

FTD