Halfword PowerPoint PPT Presentations

All Time

Recommended

The ARM Architecture Halfword access and signed halfword/byte accesses were added to the architecture in v4T, this is the reason the offset field is not as flexible ...

| PowerPoint PPT presentation | free to view

LW R1, 30(R2) Load word. LH R1, 40(R3) Load halfword. LHU R1, 40(R3) Load halfword unsigned ... small code size (30% smaller?) More Recent Performance Benefit: ...

| PowerPoint PPT presentation | free to view

Designs the ARM range of RISC processor cores ... Halfword means 16 bits (two bytes) Word means 32 bits (four bytes) ... All instructions must be halfword aligned ...

| PowerPoint PPT presentation | free to view

College of Computer Sciences and Engineering. King Fahd University of Petroleum and Minerals ... Halfword address should be a multiple of 2 .ALIGN n directive ...

| PowerPoint PPT presentation | free to download

Are there any significant problems that people are running into? ... Word, HalfWord, and Dword - Varies by machine, but today a 'standard word' would ...

| PowerPoint PPT presentation | free to download

Most-significant byte at least address of a word. c.f. ... lb, lh: extend loaded byte/halfword. beq, bne: extend the displacement ...

| PowerPoint PPT presentation | free to download

8 (byte), 16 (halfword), 32 (word) and 64 (doubleword) length data types ... Use of Stack. Exercise For Reader. Find out about instruction set for Pentium and PowerPC ...

| PowerPoint PPT presentation | free to view

QuadCore Team DLX ISA David Bild Greg Bok Jake Czyz Brandon Keao Floating-Point Instructions There are three categories for the DLX floating-point instructions ...

| PowerPoint PPT presentation | free to download

Embedded market study

| PowerPoint PPT presentation | free to download

Find out what this instruction is about (using the opcodes table) OPCODE = 1 Byte ... The 'z' refers to zero, which is the ASCII code for the null character. ...

| PowerPoint PPT presentation | free to view

(Computer Architecture) *

| PowerPoint PPT presentation | free to view

Accessing Memory Chapter 5 Lecture notes for SPARC Architecture, Assembly Language Programming and C, Richard P. Paul by Anu G. Bourgeois * Memory Addresses are 32 ...

| PowerPoint PPT presentation | free to download

ACT is a complete environment for testing compliance to the AMBA spec. ... In addition to our partnering with semiconductor companies, ...

| PowerPoint PPT presentation | free to download

William Stallings Computer Organization and Architecture 7th Edition Chapter 10 Instruction Sets: Characteristics and Functions

| PowerPoint PPT presentation | free to view

William Stallings Computer Organization and Architecture 6th Edition Chapter 10 Instruction Sets: Characteristics and Functions

| PowerPoint PPT presentation | free to view

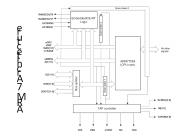

ARM7 Architecture Memory signals MAS[1:0]: bus encodes the size of the transfer. The ARM7TDMI processor can transfer word, alfword, and byte quantities.

| PowerPoint PPT presentation | free to download

Title: The ARM Architecture Author: ARM Training Last modified by: Jeff Created Date: 12/11/1995 11:10:42 AM Document presentation format: On-screen Show (4:3)

| PowerPoint PPT presentation | free to view

ARM7TDMI processor The ARM7TDMI processor is a member of the Advanced RISC machine family of general purpose 32-bit microprocessor What does mean ARM7TDMI ?

| PowerPoint PPT presentation | free to download

William Stallings Computer Organization and Architecture 7th Edition Chapter 10 Instruction Sets: Characteristics and Functions What is an Instruction Set?

| PowerPoint PPT presentation | free to download

William Stallings Computer Organization and Architecture 8th Edition Chapter 10 Instruction Sets: Characteristics and Functions What is an Instruction Set?

| PowerPoint PPT presentation | free to view

... code size * This training module provides an introduction to the ARM7TDMI processor embedded in the AT91 series of microcontroller. we ... 16bit 32bit ...

| PowerPoint PPT presentation | free to view

PC-relative to allow position independent code, and allows restricted branch range to jump to nearby addresses. How to access full 32-bit address space?

| PowerPoint PPT presentation | free to download

William Stallings Computer Organization and Architecture 6th Edition Chapter 10 Instruction Sets: Characteristics and Functions What is an instruction set?

| PowerPoint PPT presentation | free to view

EE 319K Introduction to Embedded Systems Lecture 4: Data structures, Finite state machines

| PowerPoint PPT presentation | free to download

What is an instruction set? The complete collection of ... Ordinal - unsigned integer. Unpacked BCD - One digit per byte. Packed BCD - 2 BCD digits per byte ...

| PowerPoint PPT presentation | free to view

add, branch, load/store. multiply, divide, sqrt. mmx_add. What storage locations? ... Retrieves 8-bit value from memory location ($4 1000) and puts the result into $3 ...

| PowerPoint PPT presentation | free to view

Designs the ARM range of RISC processor cores ... to semiconductor partners who fabricate and sell to their customers. ARM does not fabricate silicon itself ...

| PowerPoint PPT presentation | free to view

An Efficient SoC Test Technique by Reusing On/Off-Chip Bus Bridge Adviser: Chao-Lieh Chen Student: Shih-Hao Lin 0052802 Yi-Ming Huang 0052811

| PowerPoint PPT presentation | free to view

William Stallings Computer Organization and Architecture 8th Edition Chapter 10 Instruction Sets: Characteristics and Functions What is an Instruction Set?

| PowerPoint PPT presentation | free to download

No las veremos (al menos por ahora.) Instrucciones para tratamiento de excepciones. Las veremos mas adelante. Instrucci n NOP: no hace nada. ...

| PowerPoint PPT presentation | free to view

CS 300 Lecture 8. Intro to Computer Architecture / Assembly Language ... Mips: and, andi, or, ori, nor. How do we use these with bit field constants? Shifting ...

| PowerPoint PPT presentation | free to download

In machine code each instruction has a unique bit pattern ... Decrement (a--) Negate (-a) 24. Shift and Rotate Operations. 25. Logical. Bitwise operations ...

| PowerPoint PPT presentation | free to view

Two separate instruction sets, 32-bit ARM instructions and 16-bit Thumb instructions ... Return with : MOVS pc, lr. Prefetch Abort ...

| PowerPoint PPT presentation | free to view

The University of Texas at Austin. Austin, TX 78712-1084. http://signal.ece.utexas.edu ... 16 32-bit registers per data path (A0-A15 and B0-B15) ...

| PowerPoint PPT presentation | free to download

Original Author:Adrian J Pullin Adapted by: Chi-Cheng Lin, Winona State University ... In machine code each instruction has a unique bit pattern ...

| PowerPoint PPT presentation | free to view

William Stallings Computer Organization and Architecture 8th Edition Chapter 10 Instruction Sets: Characteristics and Functions What is an Instruction Set?

| PowerPoint PPT presentation | free to view

Lecture 8 Sept 23

| PowerPoint PPT presentation | free to download

William Stallings Computer Organization and Architecture 8th Edition Chapter 10 Instruction Sets: Characteristics and Functions 22 23 24 25 27 28 29 29 30 Stack Frame ...

| PowerPoint PPT presentation | free to view

The DLX Architecture CS448 Chapter 2 DLX (Deluxe) Pedagogical world s second polyunsatured computer via load-store architecture Goals Optimize for the common ...

| PowerPoint PPT presentation | free to download

COE 1502 Memory Model Introduction Our current processor uses a memory interface with the assumptions: Interface signals MemRead, MemWrite, MemoryAddress ...

| PowerPoint PPT presentation | free to download

The DLX Architecture. CS448. Chapter 2. DLX (Deluxe) Pedagogical 'world's second polyunsatured computer' via load-store architecture. Goals ...

| PowerPoint PPT presentation | free to download

We're going to use the MIPS R2000 instruction set for the projects in this course ... symbolic address (that you declare in SPIM) symbolic address with register index ...

| PowerPoint PPT presentation | free to download

Schedules across branches ... between performance improvement and branches replaced by RFUOP's. Benchmarks with lowest branch reduction have lowest speedup ...

| PowerPoint PPT presentation | free to download

Title: Interrupts & Input/output Author: S. Dandamudi Last modified by: Sivarama Dandamudi Created Date: 11/24/1998 12:49:00 AM Document presentation format

| PowerPoint PPT presentation | free to download

bytes: 8 bits. Registers are words, 32 bits each. lw, sw are word operations ... How many instruction formats? 3 in MIPS, we'll look at 2 now. CS 141 Chien ...

| PowerPoint PPT presentation | free to view

RISC vs CISC instruction-set design philosophy. June 2005 ... Add, Subtract, and Specification of Constants ... Conditional branches use PC-relative addressing ...

| PowerPoint PPT presentation | free to download

Java stops the translation at the byte code level. The Java virtual machine, which is at the assembly language level, interprets ...

| PowerPoint PPT presentation | free to view

Memory access is available only for load and store instruction ... A range of memory locations is logically replaced by device registers ...

| PowerPoint PPT presentation | free to download

Accumulator is only really beneficial for a chain (sequence) of calculations ... Add, subtract, shift can only be done to A (8-bit accumulator) ...

| PowerPoint PPT presentation | free to download

To be used with S. Dandamudi, 'Introduction to Assembly Language ... Chapter 13: Page 3. Instruction Format. load, arithmetic/logical. with immediate operands ...

| PowerPoint PPT presentation | free to view

(orginal note from Dr. Robert F. Hodson) (based on notes by Randy Katz) 2 ... Effective Address How is memory location specified? ...

| PowerPoint PPT presentation | free to view

Chapter 2 Instructions: Language of the Computer The University of Adelaide, School of Computer Science * Chapter 2 Instructions: Language of the Computer * The ...

| PowerPoint PPT presentation | free to download

Lecture 8: Instruction Set Architecture & Pipelining. Computer Engineering ... DLX (DELUXE): Load/store architecture. Similar to a typical RISC processor MIPS. ...

| PowerPoint PPT presentation | free to view

Compile with '-g' (keep full symbol table) Don't use compiler optimization ('-O', ' O2' ... On a core (post-mortem) gdb progname core ...

| PowerPoint PPT presentation | free to download

Need translation to a lower-level computer understandable format ... With an ALU and fetch-decode unit, we have the equivalent of Babbage's computation engine ...

| PowerPoint PPT presentation | free to download

memory access is available only for load and store instruction ... a range of memory locations is logically replaced by device registers ...

| PowerPoint PPT presentation | free to view