Src1 PowerPoint PPT Presentations

All Time

Recommended

Gestion de projet en SRC1 Enseignement au 1er semestre; 2 CM, 5 TD, 3 TP; 1 note l crit; * * L organisation de ce module D finition des principaux termes ...

| PowerPoint PPT presentation | free to view

Mise en uvre des Protocoles TCP/IP Cours R seaux SRC1 IUT Cherbourg-Manche antenne de Saint-L Rappel : Qu est ce qu un protocole ? C est la description des ...

| PowerPoint PPT presentation | free to download

State = pc, ra,rb. Instruction = opcode, target, src1, src2. ISA (Instruction Set Architecture) ... 0 add rb ra ra. 1 add ra rb ra. Step ISA MA Inst 0 Inst1. 0 ...

| PowerPoint PPT presentation | free to view

For an implementation of the full MIPS ISA ... Seq'ing. PCWrite control. Memory. Reg control. SRC2. SRC1. ALU control. Label (Addr) Decode (1) ...

| PowerPoint PPT presentation | free to view

Low-Complexity Reorder Buffer Architecture* Gurhan Kucuk, Dmitry Ponomarev, Kanad Ghose Department of Computer Science State University of New York

| PowerPoint PPT presentation | free to download

Title: Autonomous Networks Research Group: Vision and Plans Author: Bhaskar Krishnamachari Last modified by: Dongjin Son Created Date: 11/9/2003 4:38:04 AM

| PowerPoint PPT presentation | free to view

Instruction-Level Parallelism (ILP) is a set of techniques for executing ... how your code is structured affects. how much ILP the compiler and the. CPU can give you. ...

| PowerPoint PPT presentation | free to download

EECS 322: Computer Architecture Single-cycle Multi-cycle FSM controller Multi-cycle microcontroller

| PowerPoint PPT presentation | free to download

Title: One-to-one m Author: Retana, Alvaro Last modified by: Alvaro Retana Document presentation format: On-screen Show (4:3) Other titles: Arial SimSun Bookman Old ...

| PowerPoint PPT presentation | free to download

stall. isaAlu. Goal: Establish Pipeline refines ISA ... stall. isaAlu. witnessed refinement. isaRegFile. isaAlu. Limitation: State explosion. isaRegFile ...

| PowerPoint PPT presentation | free to download

So a 2 GHz processor has 2 billion clock cycles per second. ... What's the Relevance of Cycles? ... stage takes, say, one CPU cycle, then once the loop gets ...

| PowerPoint PPT presentation | free to download

Title: Author: Last modified by: Created Date: 11/21/1998 12:05:06 AM Document presentation format

| PowerPoint PPT presentation | free to view

COE 308 MIPS Instructions MIPS Instructions in MIPS Reduced Instruction Set 3 Operands per operation: 2 sources and 1 destination Most instructions are of the form ...

| PowerPoint PPT presentation | free to download

Stream Processing in Networks of Smart Devices Holger Ziekow, Lenka Ivantysynova Institute of Information Systems Humboldt University of Berlin, Germany

| PowerPoint PPT presentation | free to download

Spectrum in terms of tones of H(1) 9. Advantages of Spectral BIST System. System uses Zhang et al.'s spectral test pattern generator in sequential mode ...

| PowerPoint PPT presentation | free to view

Dongjin Son, Bhaskar Krishnamachari (USC/EE), and John Heidemann (USC/ISI) 2. Motivation ... Zhao, Ganesan, Aguayo, Cerpa, Woo, Lal, Zuniga, Son, etc. ...

| PowerPoint PPT presentation | free to view

Supercomputing in Plain English An Introduction to High Performance Computing Part II: The Tyranny of the Storage Hierarchy Henry Neeman, Director OU Supercomputing ...

| PowerPoint PPT presentation | free to download

find a different representation for the FSM instead of circles and arcs! ... unconditional branch (e.g. back to F1 in FSM) dispatch (e.g. multi-way based on IR decode) ...

| PowerPoint PPT presentation | free to view

Remember, if all else fails, you always have the toll free phone bridge to fall back on. ... any time after 2:00pm. Please connect early, at least today. ...

| PowerPoint PPT presentation | free to download

Multi-purpose programmable solution. Standard video/audio (en/de)-coders ... Proprietary video enhancement processing to improve picture quality. Eg. ...

| PowerPoint PPT presentation | free to view

Spectral BIST Alok Doshi Anand Mudlapur Overview Introduction to spectral testing Previous work Application of RADEMACHER WALSH spectrum in testing and design of ...

| PowerPoint PPT presentation | free to download

Random logic, programmable logic array (PLA), or ROM. Fast. Inflexible. Firmware. Microprogrammed or microcoded CU. Control implemented like a computer (microcomputer) ...

| PowerPoint PPT presentation | free to view

Lecture 19: SIMD and Multimedia Extensions Mary Hall November 13, 2012 11/13/2012 CS4230

| PowerPoint PPT presentation | free to download

An Extensible Model-Based Mediator System with Domain Maps Amarnath Gupta* Bertram Lud scher* Maryann E. Martone+ *San Diego Supercomputer Center (SDSC)

| PowerPoint PPT presentation | free to download

SYNTHESIS OF APPLICATION SPECIFIC VLIW PROCESSORS. Under the supervision of. Prof. Anshul Kumar ... Identification of custom FUs for a given application ...

| PowerPoint PPT presentation | free to view

Parallel Programming & Cluster Computing Stupid Compiler Tricks Henry Neeman, University of Oklahoma Charlie Peck, Earlham College Andrew Fitz Gibbon, Earlham College

| PowerPoint PPT presentation | free to download

Title: Calvin & Kathryn s Wonderful Group Author: CSCF Last modified by: Kathryn Mckinely Created Date: 9/27/2001 8:35:48 PM Document presentation format

| PowerPoint PPT presentation | free to download

Bind a variable to a package to override the access mechanism ... usr/bin/perl. use strict; use warnings; use CatchOut; print 'Start capturing STDOUTn' ...

| PowerPoint PPT presentation | free to download

... in Software Development Project. Lattice QCD extremely ... Foster 'Linux style' contributions to level 3 API ... (new documentation and revision) ...

| PowerPoint PPT presentation | free to download

Complete control of transform and lighting HW. Complex vertex ... Swizzling. 38. Vertex Programming. Assembly Language. Source registers can be negated: ...

| PowerPoint PPT presentation | free to view

Department of Electrical and Computer Engineering. Auburn University, Auburn, AL 36849 ... Control implemented like a computer (microcomputer) Microinstructions ...

| PowerPoint PPT presentation | free to view

Title: CS434/534: GNU Radio Author: Yang Richard Yang Last modified by: Richard Yang Created Date: 2/16/1997 2:02:43 PM Document presentation format

| PowerPoint PPT presentation | free to view

ASIP: optimal balance between : reuse opportunities, computational efficiency, ... Design time is critical. Refinement and profiling based design-flow ...

| PowerPoint PPT presentation | free to view

Weihua Sheng, Jianjiang Ceng, Manuel Hohenauer, Hanno ... Verilog. SystemC. Wrapper. Simulator. Generator. RTL Code. Generator. Assemb./Linker. Generator ...

| PowerPoint PPT presentation | free to view

Functional verification is a major bottleneck ... Source: Tom Schubert, Intel, DAC 2003. 7855. 2240. 800. 25000. Pentium. Pentium Pro. Pentium 4 ...

| PowerPoint PPT presentation | free to download

Register Ri. Register Rj. Register Rk. operand. operand. result. Operation circuitry ... Main memory typically maps into cache in one of three ways: Direct ...

| PowerPoint PPT presentation | free to download

Computer Network Lab. AQM's Advantages for Responsive Flows ... Computer Network Lab. Random Early Detection. An active queue management ...

| PowerPoint PPT presentation | free to view

Center for Embedded Computer Systems ... Functional verification is a major bottleneck ... Bottlenecks of Functional Verification. Lack of high-level models ...

| PowerPoint PPT presentation | free to download

Supercomputing in Plain English Part VIII: Multicore Madness Henry Neeman, Director OU Supercomputing Center for Education & Research University of Oklahoma ...

| PowerPoint PPT presentation | free to download

2001-2003 Howard Huang ... My office hours, move to Mon or Wed? Plan: Pipelining this and next week, maybe performance analysis

| PowerPoint PPT presentation | free to download

Part VII Advanced Architectures

| PowerPoint PPT presentation | free to view

Schedules across branches ... between performance improvement and branches replaced by RFUOP's. Benchmarks with lowest branch reduction have lowest speedup ...

| PowerPoint PPT presentation | free to download

OU Supercomputing Center for Education & Research. University of Oklahoma ... Core Duo (Yonah), a cache miss makes the program stall (wait) at least 48 cycles ...

| PowerPoint PPT presentation | free to download

Faults detected per iteration for b12 benchmark circuit. 22. To be continued on Tuesday 11/16 . calculate either the auto-correlation of testing responses ...

| PowerPoint PPT presentation | free to download

Three operands except for load/store. Load: load data from memory to register ... STORE r1,I ; I = r1. M68000 (If both I and J are memory locations) MOVE J,D0 ; D0 = J ...

| PowerPoint PPT presentation | free to view

Supercomputing in Plain English An Introduction to High Performance Computing Part IV:Stupid Compiler Tricks Henry Neeman, Director OU Supercomputing Center for ...

| PowerPoint PPT presentation | free to download

Mircea Stan, Kevin Skadron, David Brooks, Lev Finkelstein, Antonio Gonz lez 2004 ... What current chips do (Lev) HotSpot (Kevin) 2 ...

| PowerPoint PPT presentation | free to download

compute branch target (PC sign_ext(IR[15-0]) 2)) and store it in ALUOut. use rs and rt to read RegFile and store output in A and B ...

| PowerPoint PPT presentation | free to view

Functional Coverage Driven Test Generation for Validation of ... Source: Tom Schubert, Intel, DAC 2003. 7855. 2240. 800. 25000. Pentium. Pentium Pro. Pentium 4 ...

| PowerPoint PPT presentation | free to download

Title: Bluespec technical deep dive Author: Nikhil Last modified by: Arvind Created Date: 1/21/2003 7:25:41 PM Document presentation format: On-screen Show

| PowerPoint PPT presentation | free to download

GNU Radio Software. Opensource software (GPL) Don't know how something works? Take a look! ... GNU Radio Hardware. Sends/receives waveforms. USRP Features. USB ...

| PowerPoint PPT presentation | free to view

Shuvendu K. Lahiri Sanjit A. Seshia Randal E. Bryant Carnegie Mellon University, USA Processor Verification Views of System Operation Instruction Set Instructions ...

| PowerPoint PPT presentation | free to download

Op-code Lookup. Symbol Table Lookup. Generate. Machine Code. Example. 1 OPT CRE. 2 00000019 A: EQU 25 ... Area EQU Length*Width. ORG (ORiGin) Sets up value of ...

| PowerPoint PPT presentation | free to download

| PowerPoint PPT presentation | free to download

snk b('b', O, 'out.dat'); OCAPI Classes: 3- Internal Signal ... create fx-p FSM description and run timed simulation to generate the VHDL code. ...

| PowerPoint PPT presentation | free to download

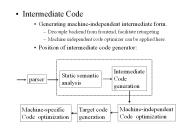

Intermediate Code Generating machine-independent intermediate form. Decouple backend from frontend, facilitate retargeting Machine independent code optimizer can be ...

| PowerPoint PPT presentation | free to download