Encryption Transaction with 3DES - PowerPoint PPT Presentation

1 / 29

Title:

Encryption Transaction with 3DES

Description:

D Latch. 2:1 Multiplexor. D Flip Flops. Enable / Reset asserted high ... 32'b Latch. 32'b Exclusive OR. 32'b 2:1 Multiplexor. PC1 Permutation. 64'b Text Register ... – PowerPoint PPT presentation

Number of Views:62

Avg rating:3.0/5.0

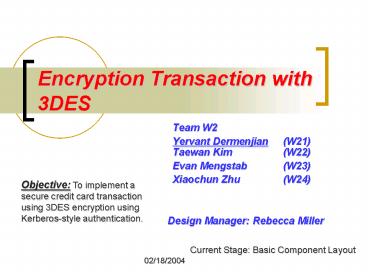

Title: Encryption Transaction with 3DES

1

Encryption Transaction with 3DES

- Team W2

- Yervant Dermenjian (W21)Taewan Kim (W22)

- Evan Mengstab (W23)

- Xiaochun Zhu (W24)

Objective To implement a secure credit card

transaction using 3DES encryption using

Kerberos-style authentication.

Design Manager Rebecca Miller

Current Stage Basic Component

Layout 02/18/2004

2

Current Status

- Design Proposal (100 done)

- Architecture Proposal (100 done)

- Size Estimate and Floor Plan (100 done)

- Full-chip Transistor-level Schematic (100 done)

- Component Layout

- Another new Floor Plan

- Basic components (100 done)

- Layout of larger blocks (90 done)

- To be done

- Some permutations layouts

- Top-Level layout routing

- Spice Simulation

3

Revised Architecture

Sh_e

32b input

e/d

wr_en

Enc_ShiftL

32b Latch

KeyReg 56b Register

PC (wiring)

21 mux

21 mux

32b Latch

56

32b

Dec_ShiftR

Sh_d

key_in

Sub_rnd

32

64

R

IP-1 wiring

OUT ready

21 mux

L

PC-2 Wiring 56-gt48

ready

txt_in

Expand 32-gt48 wiring

32

48

Text 64b Register

IP wiring

21 mux

64

32

L

P 32-gt32 wiring

32

S-Box 512 x 4b

R

32

32

4

Top Level des3

5

Updated Floorplan

M1 M2 M3 M4

360µm

Input

Mux

Left Shift

32b Latch

Mux

Mux

Mux

32b Text Register (L)

32b Text Register (R)

48b XOR

SBOX

IP

IP-1

P

32b Mux

PC1

56b Key Reg

PC2

32b XOR

Expand

Right Shift

Output

All large functional blocks use Metal 1 and Metal

2.

32b Latch

32b Mux

Left Shift

Right Shift

clock

416µm

Program Control

6

Pin Connections / Porosity

7

Pin Connections / Porosity

8

Project Goals

- Implement fully functioning 3DES Chip

- Speeds high enough for credit card transactions

- Dense design for small area

9

Inverter / Buffer

10

Exclusive OR

11

D Latch

12

21 Multiplexor

13

D Flip Flops

Enable / Reset asserted high

No Enable / Reset asserted high

14

Half Adder

15

Left Barrel Shifter

16

Right Barrel Shifter

17

Program Control

18

56b Key Register

19

32b Latch

20

32b Exclusive OR

21

32b 21 Multiplexor

22

PC1 Permutation

23

64b Text Register

24

SBOX1 ROM

25

Updated Transistor Counts and Area

26

Updated Transistor Counts and Area

27

Updated Transistor Counts and Area

Area 0.2028 mm2

Transistors 15,238

Density 0.08 trans/µm2

28

Design Decisions

- Stick with hardwiring for permutations

- Inputs and outputs on same side

- Layed out in one long row of skinny modules

29

Questions

?