D0 Trigger Status - PowerPoint PPT Presentation

1 / 18

Title:

D0 Trigger Status

Description:

Loss of senior engineer, Steve Gross. Loss of engineer, Kirsten Moore. Replacement uncertain ... 5 days to stuff & check. Installation/Commissioning ... – PowerPoint PPT presentation

Number of Views:41

Avg rating:3.0/5.0

Title: D0 Trigger Status

1

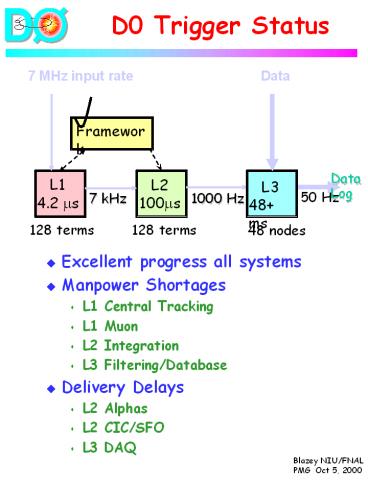

D0 Trigger Status

7 MHz input rate

Data

Framework

Data Log

L2 100ms

L1 4.2 ms

L3 48 ms

50 Hz

7 kHz

1000 Hz

48 nodes

128 terms

128 terms

- Excellent progress all systems

- Manpower Shortages

- L1 Central Tracking

- L1 Muon

- L2 Integration

- L3 Filtering/Database

- Delivery Delays

- L2 Alphas

- L2 CIC/SFO

- L3 DAQ

2

Framework Status

- Components(MSU)

- Operational

- Installation/Commissioning

- Support detector commissioning

- Completing readout to L3

- Integrating with L2

- Firmware

- Completion of pseudo-terms

- Commissioning run-control

- Personnel

- Loss of senior engineer, Steve Gross

- Loss of engineer, Kirsten Moore

- Replacement uncertain

- Schedule

- Complete Readout to L3 1/11

- L2 trigger mask and pseudo-terms deferred?

Good progress, on time

3

Detector/L1/L2 Components

L1 LUM

LUM

L2Cal

CAL

L1 FPS

L2PS

FPS

Global L2

CFT/ CPS

L1 CTPT

L2CFT

L2STT

SMT

L2 Muon

L1 Muon

Muon

L2FWCombined objects (e, m, j)

L1FPD

FPD

L1FW towers, tracks, correlations

4

Luminosity Monitor Status

- Components(Brown)

- Scintillator(48) Complete

- Electronics

- CAFÉ boards(175) on hand

- Completing ADC(12) board layout, ordering parts

- Vertex board, FPGA 75 complete, layout

commencing. - Procuring signal cables(60) soon

- Crate/PS on hand

- Installation/Commissioning

- Installed Scintillator 4/00

- Cabling awaits FPS.

- Commissioning thereafter

- Software

- Working on embedded software

- Download currently underway.

- Database under development

- Schedule

- February 1, Electronics Installed

- March 1, Luminosity Monitoring

Good progress, on time

5

L1CTPT/FPS

6

L1 CTPT/FPS Status

- Components

- Analog(Fermilab-D0)

- AFE-8MCM (primarily CFTax) At vendor, full order

complete 1/01 - AFE-12MCM (primarily FPS)

- motherboard prototype this month

- daughter prototype board order 1/01

- Crates/Cables on hand

- Power supplies delayed until new year (partial).

- Mixer(Fermilab-CD)

- Super-sector (1/5th) 11/15

- Full Mixer 1/01

- Digital(Fermilab-D0)

- Motherboard here

- Transition module 1/11

- CTPT daughter boards 11/15

- FPS daughter board order out, parts on order

- Crates/Cables/PS here

- Installation/Commissioning

- Assembling test stands for digital/VHDL testing

7

L1 CTPT/FPS Status

- Firmware

- AFE Mixer complete

- DFE 50

- Collector/Broadcaster 50

- No diagnostics

- Personnel

- Recently lost Kin Yip (FNAL postdoc) Juan

Lizarazo (FNAL Co-op) both on VHDL - A position has been available but not yet filled

a new student arrived. - Reduced engineering (John Anderson) has delayed

AFE12. - Have redirected Jamieson Olsen to assist with

VHDL, but need technical help to assist with

reorganization and installation. - Schedule

- Analog

- 10 AFE8 installed, operating 12/00

- Balance by 2/01

- AFE12 unknown (in prototype)

- Supplies as arrive

- Digital

- Sufficient hardware for commissioning

- Balance Installed by 12/00

Good progress on all fronts AFE12, VHDL concerns

8

L1 CAL Status

- Components

- Analog pick-offs (320) to accommodate changed BW

prototyped. 1FTE month to production - Quadrant hardware (40) circuit/firmware designed

- L2/L3 Readout complete

- Installation/Commissioning

- Inactive until framework complete 11/00

- Firmware

- All exists, not all tested

- Personnel

- Same as framework

- Schedule

- Within a month progress should resume

- Start w/ analog pick-offs

- L2 L3 readout 11/00

Late but well before 3/01

9

L1 MUON Status

- Components

- L1MuTrigger (4 crates) Prod Beginning(UAz)

- Motherboard starting production/fabrication

- Scintillator daughter board preproduction in

assembly - Wire daughter board production board in design

- Crate Manager testing production card, balance to

be assembled - Trigger Manager daughter-board starting prod/fab

now - Serial Link Transmitters complete

- Serial Link Receivers production testing

- MCEN (5 crates) in Preprod Testing(BU)

- MCEN preproduction testing underway

- Centroid Daughter Board preprod testing underway

- Crate manager preprod layout.

- Crates/Backplanes complete

- Power Supplies on order.

- Installation/Commissioning

- One trigger, one manager crate in operation and

readout. - Next providing L1CTPT Manager Crate.

- Two Octants triggering by 11/00

10

L1 Muon Status

- Software

- Download Infrastructure in place

- Preproduction versions of all firmware exist.

- No alarms, monitoring

- Personnel

- Arizona down to zero from two postdocs.

Advertising for one replacement - Boston post doc hired, visa difficulties

- Discussing Ken Johns buy-out.

- Need help w/ assembly/test of PSupplies

- Schedule

- L1 Muon full crate commissioned 1/01

- MCEN full crate commissioned 3/01

L1Muon before 3/01 Some concern MCEN, manpower

11

L2 Component Status

- Alpha serial processors (MSU,UM,UIC)

- Production Status

- preproduction worked out-of-the-box

- ADCO, same vendor that produced CDF TDCs

- About 30 stuffed or nearly stuffed

- Parts for another 15 in reserve

- Many key components obsolete

- Diagnostics _at_ UM

- Four boards

- To our knowledge none work

- Diagnostics _at_ UIC

- 10 boards

- 2 incorrectly mounted components

- 5 have partial functionality (1 close, others

unknown) - Considering a range of options

- Repair sufficient boards for March 1, 2001

- Build new boards with larger vias and reserve

parts - Build new boards with larger vias. Recover

components and build full complement. - Re-layout board and/or find new vendor

12

L2 Components Cont.

- MBT I/O Cards(U-Maryland)

- 6 production cards received. 3 pass specs. 3

under test now - Firmware functionality 90 done.

- Remaining 25 boards built, parts on hand

- Balance after Oct. tests.

- FIC L1/L2 Interface(SACLAY)

- Boards complete

- Final firmware adjustments October 16-20.

- SLIC Parallel Proc.(NIU,Columbia)

- Boards complete

- First results from DSP Central algorithm meet

speed/efficiency requirements - CIC, SFO Muon/L2 Interface (U-Neb)

- Prototypes pass battery of tests but not up to

standard design practices (two layers,

unconventional shielding planes, unequal traces

on differential signals...) - Have solicited advice from Fermilab engineers but

process delayed by illness. Restarting now. - Delivery unknown

13

L2 Status Cont.

- Software

- C Framework exists

- Preprocessor algorithms well developed, global

needs attention. - Installation/Commissioning

- MCH and test stand racks and crates 85 done.

Cabling 65 done - Commissioning sequence under discussion.

- Personnel

- Recently lost one key postdoc from UIC and one

from Maryland, will lose another UIC postdoc at

the end of the year - One UIC postdoc has been replaced and new ones

added from MSU and Columbia - Lack of on-site coordinator has slowed progress.

Discussing Nikos Varelas buy-out. - Lack of project engineer has slowed progress.

However, Rich Kwarciany (CD Electronics System

Engineer) has been a great help as an on-call

consultant. - Schedule

- Essentially on hold until alpha, CIC, SFO issues

resolved. - Once alphas MBTs are on hand the L2CAL, L2CTT,

L2PS can be assembled lt1 month.

MBT, SLIC, FIC ready before 3/01 Alpha, CIC/SFO,

manpower concerns

14

DAQ/L3

- Evolved to a single multipurpose card used in

VRC, SB, processor nodes (100) - VHDL code specific to VRC, SB, Node complete

- ETG is one of a kind.

15

L3/DAQ Status

- Components(Brown)

- Layout done for 6 wks, parts procurement

difficult. - 25 board order placed with vendor

- Layout _at_ board houses. Bids received. Production

complete lt 2 weeks. - Procuring parts now

- 5 days to stuff check

- Installation/Commissioning

- Maintaining emulators for commissioning, no

schedule delay for other systems. - Cable plant is minimal - reuses infrastructure,

MCH 50 done, remainder under discussion. - Software(Brown,Washington)

- Framework up and running

- Nodes also operational

- Schedule (full chain by Jan 1)

- After receipt of board 1-2 week at Brown, then

install 4 VRCs _at_ DAB - 2 wks install 1 SB, fiber between VRC-SB

- 2 wks install multiple node adapters, fiber

between SB-node. - ETG January

Software in good shape Watching delivery closely

16

Filtering/Database

- Components(Various Institutions)

- Operational version of ScriptRunner

- Unpacking code for cal, smt and muon

- electron, muon, jet, missing et, and tau tools

- Database and interface in design.

- Installation/Commissioning

- Participating in online tests of PDTs, CFT.

- Participating in 10 SiDet Test

- Personnel

- Impending departure of Charles Leggett (LBL)

infra-structure (unpack,tool template,offline

verification) - Carmem Silva (LAFEX) database, currently only

1FTE on database - Insufficient support for NT release porting.

- Schedule

- 11/00 standard running including ScriptRunner in

Mark Pass mode - 1/01 monitor displays available

- 3/01 operational versions of all physics tools

ported and available

Filtering operable, needs manpower

17

Reportable Milestones

Priorities (1) FWK, L1mu, L1CAL, L3 (2)

L2Global, L2CAL (3) L1L2 CTPT, FPS

18

Manpower Needs

- To free engineers for VHDL preparation a senior

technician to assist CTPT construction. Could

also help with L1Muon, L2 installation. - An engineer to assist L2 debugging integration.

This could be considered an escalation of the

already valuable on-call arrangement. - Arrange full-time contributions for

- Ken Johns L1Muon

- Nikos Varelas L2

- Two programmers for

- L3 infrastructure/release

- Database