Device Interface Board for Wireless LAN Testing - PowerPoint PPT Presentation

1 / 41

Title:

Device Interface Board for Wireless LAN Testing

Description:

DUT Device under test (positive edge D flip-flop) ... Figure 6 D flip-flop circuit schematic. Project Overview. Limitations. 27 C - 33 C ... – PowerPoint PPT presentation

Number of Views:29

Avg rating:3.0/5.0

Title: Device Interface Board for Wireless LAN Testing

1

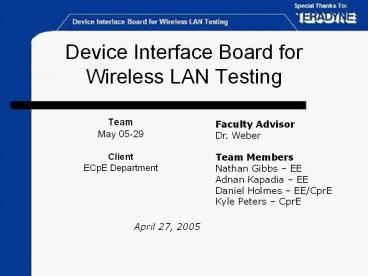

Device Interface Board for Wireless LAN Testing

- Team

- May 05-29

- Client

- ECpE Department

Faculty Advisor Dr. Weber Team Members Nathan

Gibbs EE Adnan Kapadia EE Daniel Holmes

EE/CprE Kyle Peters CprE

April 27, 2005

2

Presentation Outline

- Resources and Schedule

- Resource requirements

- Schedule

- Closure Materials

- Project Overview

- Introduction

- Problem statement

- Operating environment

- Intended user(s) and use(s)

- Assumptions and limitations

- End product

- Project Activities

- Present accomplishments

- Future goals

- Approaches considered and one used

- Project definition activities

- Research activities

- Design

- Test and implementation

3

Definitions

- DUT Device under test (positive edge D

flip-flop) - Header Preamble bits sent prior to the sending

of information in a data packet

Figure 1 Data Packet and Header

- Data packet Group of bits sent through a

communication channel sequentially - FPGA Field programmable gate array

- Tx/Rx Transmitter/reciever

4

Project Overview

5

Acknowledgement

- Teradyne

- Dr. Weber

- Advice

- Carver Lab

6

Introduction

- Teradyne Integra J750

- Digital Tester

- Donated to Iowa State

- Desire to test wireless chips using J750

- Project is first step toward that goal

- Project created wireless interface to test

digital device remotely

Figure 2 Teradyne Integra J750

7

Project Overview

- Problem Statement

- Problem

- Prove J750 can perform wireless test on a device

- Solution

- Develop wireless interface to J750

- Develop test for DUT

- Solve latency and data transmission issues

?

Figure 3 Project Problem

8

Project Overview

- Operating Environment

- 27C - 33C

- ESD wristbands

- IG-XL for Windows

Figure 4 ESD Wristband

9

Project Overview

- Intended Users

- ISU ECpE Faculty and Students

- Intended Uses

- Functional test of a digital device

- (Future) Wireless chipset test

10

Project Overview

- Assumptions

- System

- Teradyne J750 can capture output despite delay

introduced by wireless network - User

- Manual, or experience with J750

- Experience with an FPGA and Verilog

- Understand the DUT operation

Figure 5 FPGA

Figure 6 D flip-flop circuit schematic

11

Project Overview

- Limitations

- 27C - 33C

- Digital I/O only

- Wireless components limit data rate

- J750 cannot be moved

- Rx/Tx range 50 feet

12

Project Overview

- End Product and Other Deliverables

- Wireless interface

- Demonstration of wireless test

- Manual for wireless test operation

Figure 8 Cover page of wireless manual

13

Project Activities

14

Project Activities

- Project Definition

- Initially wanted to test wireless chipset

- Redefined project as proof-of-concept that J750

can wirelessly test a device

15

Project Activities

- Research Activities

- Feasibility of testing wireless components with

J750 - Researched J750 setup and test creation

- Researched wireless system implementations

16

Project Activities

Design

Figure 9 System Design

17

Project Activities

- Design Constraints

- Limited choice of frequency channels

- Lose speed from J750 data rate of TX/RX at

115kbps - Limited to one FPGA

18

Project Activities

- Present Accomplishments

- Wireless interface complete and tested

- Demonstration complete

- Manual of operation complete

Figure 11 Complete manual

Figure 10 Final Setup

19

Project Activities

- Approaches Considered

- System Design

- 2 FPGAs, 2 wireless transceivers

- 4 FPGAs, 2 wireless transmitters, 2 receivers

- 1 FPGAs, 2 wireless transmitters, 2 receivers,

parallel to serial shift registers - Advantages/Disadvantages

- Chose 3

- Only 1 FPGA available

- Simple, but effective implementation

Simple to recognize wireless packets Dedicated input and output data channels

1 X

2 X X

3 X

20

Project Activities

- Implementation

- Shift Register test on J750

- Milled and soldered Tx/Rx

- Simulataed FPGA code

- Implemented wired FPGA

- Integrated subsystems

Figure 12 Mill used to create Tx/Rx

21

Project Activities

- Testing and Implementation

- Tested each subsystem

- Integrated subsystems into final setup

- Testing form

22

Project Activities

Testing and Implementation

Figure 13 Testing form

23

Resources and Schedule

24

Resources and Schedule

Actual Resources

Figure 14 -

25

Resources and Schedule

Other Resources

Item Cost

Project Poster 65.00

D Flip-Flop (TI- SN74LVC2G74) 0.43

2 x 8-Bit Shift Registers (Fairchild 74F676) 18.24

2 x Hex Schmitt Trigger (Fairchild MM74C14N) 1.80

Supplementary Circuit Components 45.00

Teradyne Integra J750 Test System 500000.00

Transmitter (RF Monolithics TX6000) 14.00

Transmitter (RF Monolithics TX6004) 14.00

Receiver (RF Monolithics RX6000) 20.00

Receiver (RF Monolithics RX6004) 20.00

4x 50 Ohm Antennas 2.00

PCB Milling 2000.00

FPGA 200.00

Total Cost 502,400.47

Donated

130.47

Figure 15 - Resource Requirements

26

Resources and Schedule

Item Cost

Parts 130.47

Labor (11/hour) 10901.00

Total 11031.47

Figure 16 Project Costs with Labor

27

Resources and Schedule

Figure 17 Major project tasks schedule

Figure 18 Project Deliverables

28

Closing Material

29

Closing Material

- Project Evaluation

- SUCCESS

- All subsystems work as planned

- Final integrated system works

- Commercialization

- Unlikely

- Cost

- Speed

- Immobile

- Price - 200 to 1500

- RF companies

30

Closing Material

- Recommendations for Additional Work

- Clock recovery circuit

- Improve wireless data rate

- Test wireless chips

31

Closing Material

- Lessons Learned

- What technical knowledge was gained?

- Learned how to build and use wireless Tx/Rx

- FPGA implementation

- Teradyne Integra J750 usage

- Parallel?Serial conversion

- System integration

32

Closing Material

- Lessons Learned

- What went well?

- System works!

- What did not go well?

- Project definition

- Initial Teradyne J750 setup and test

- Improper daughterboard wiring

- Rx amplitude

- FPGA inputs

33

Closing Materials

- Anticipated Potential Risks

- Teradyne Integra J750 and signal latency

- Encountered Risks

- Internships

- Receiver/Transmitter delivery delays

- ESD to transmitter

34

Closing Materials

- Closing Summary

- Problem

- Solution

- Successful implementation of solution

35

Figure 19 Final System Setup

36

Output Shift Register

Figure 20 Shift Register output

37

Output - Q

Figure 21 DUT output, Q

38

Output - Qbar

Figure 22 DUT output, Qbar

39

Output Serialized Output

Figure 23 Reserialized output, 100 Q Qbar 001

40

Questions?

41

Thank You