Central Processing Unit - CPU - PowerPoint PPT Presentation

Title:

Central Processing Unit - CPU

Description:

0001 = load the Accumulator (AC) from a cell in main memory ... Add to the accumulator the data at the address aaaaa. 1 0 0. a a a a a ... – PowerPoint PPT presentation

Number of Views:171

Avg rating:3.0/5.0

Title: Central Processing Unit - CPU

1

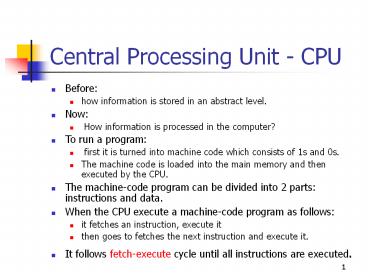

Central Processing Unit - CPU

- Before

- how information is stored in an abstract level.

- Now

- How information is processed in the computer?

- To run a program

- first it is turned into machine code which

consists of 1s and 0s. - The machine code is loaded into the main memory

and then executed by the CPU. - The machine-code program can be divided into 2

parts instructions and data. - When the CPU execute a machine-code program as

follows - it fetches an instruction, execute it

- then goes to fetches the next instruction and

execute it. - It follows fetch-execute cycle until all

instructions are executed.

2

Basic Instruction Cycle

Fetch next instruction

Execute instruction

Halt

Start

3

Component of the CPU

- Registers

- Program counter

- Accumulator

- Arithmetic Logic unit.

- Control Unit.

4

Registers

- Memory Address Register (MAR)

- Stores the address of the cell the CPU is going

to execute. - Memory Buffer Register (MBR)

- Contains instruction or data just read from the

memory. - Or data that is about to be written in the

memory. - Instruction Register (IR)

- Holds the instruction just fetched from the main

memory.

5

Program Counter - PC

- In contains the address of the next

instruction. - i.e. I 100 1101

I tells CPU to execute the instruction stored

in the address 1101.

PC 1101

6

Arithmetic Logic Unit- ALU

- It performs all arithmetic operations and Boolean

logical operations.

7

Control Unit

- It is the portion that allows things to happen.

- It controls all operations.

I tells CPU to execute the instruction stored

in the address 1101.

control unit

PC 1101

8

ALU, Registers and Control Unit Relationships

Data are presented to the ALU in registers.

Registers

Performs operations and put the result back in

registers

ALU

Control unit

Control operations.

9

CPU and System Bus

MAR

Address bus

Registers

ALU

Data bus

MBR

Control unit

Control bus

10

Instruction Format

- Op-code

- Op-code indicates what the kind of operation to

be performed. - Operands

- Specifies the things that is to be operated on

- It is an address of a cell where some data are

stored.

instruction

11

Example of Instruction

4 bits

12 bits

16-bit instruction format

0001 load the Accumulator (AC) from a cell in

main memory 0010 store the content of AC in a

cell in main memory 0101 Add to the AC the

content of a cell in the main memory For example

0001 000100000000 ? load AC with the data

stored in 000100000000.

12

(No Transcript)

13

(No Transcript)

14

Example 8-bit Processor

- Address Instruction

- 00000 001 10000

- 00001 010 10000

- 00010 100 10000

- 00011 110 10001

- 00100 111 00000

- 10000 000 00001

- 10001 000 11111

15

Six-Stage Instruction cycle

Fetch real operand From memory

Decode I

Store result In M.M

DI

FO

WO

EI

FI

Perform Operation And store Result in A register

CO

Calculate operand address

16

Reading From The Memory

17

Writing to Memory

18

Enhancing Computer Performance

- Desirable to make computers run faster.

- How can this be achieved?

- In a computer all information processing is done

in the CPU. - The speed of the CPU is the number of

micro-operations it can perform in a second.

19

CPU Speed

- CPU consists of a set of registers, an ALU and

Control Unit. - CPU micro-operations are controlled by the

control unit. - The control unit issues a sequence of control

signals at a fixed frequency. - The control unit is able to do that as it is

connected to a clock.

20

Clock

- A clock is a micro-chip that regulates the timing

and speed of all computer functions. - It includes a crystal that vibrates at a certain

frequency when electricity is applied to it. - The clock transmits a regular sequence of

alternating 1s and 0s.

21

Clock speed

- Also called clock rate, the speed at which a

microprocessor executes instructions. - Every computer contains an internal clock that

regulates the rate at which instructions are

executed and synchronizes all the various

computer components. - The CPU requires a fixed number of clock cycles

to execute each instruction. - The faster the clock, the more instructions the

CPU can execute per second. - Clock speeds are expressed in Megahertz (MHz) or

Gigahertz (GHz).

22

Control Unit - Clock

- Control unit can issue one or more control

signals in one clock cycle. - This will enable the CPU to do one

micro-operation per cycle, or a number of

micro-operations simultaneously. - Recent processor have a clock with frequency 2

GHz (2230 Hz) - (2 230 micro-operation/ sec)

23

Cache Memory

- Main memory is slower than CPU.

- There is another clock between MM and CPU to

co-ordinate the events on the system bus. - If the CPU is connected directly to the main

memory it will be slowed down by the lower clock

rate of the bus. - To ovoid this, a cache memory which can operate

at nearly the speed of the CPU is put in

between.

24

Cache and Main Memory

Word transfer

Word transfer

CPU

Cache

Main memory

- CPU repeatedly accesses a particular small part

of the main memory. - In a short time a copy of this portion of the

main memory is kept in the cache.

25

Read and Write with Cache

- Read a word from the main memory?

- The CPU checks whether the word is in the cache.

- If yes, the word is delivered to the CPU.

- If not, a block of the main memory containing the

desired word is read into the cache and then

passed to the CPU. - Write data to the main memory?

- The CPU writes the data to the cache.

- Then, the cache writes the data to the main

memory.

26

Pipelining

- Introducing parallelism into the sequential

machine-instruction program. - A number of instructions can be executed in

parallel. - Programs can run faster.

27

How does the CPU runs a program?

- The CPU runs a program by repeatedly performing

an instruction cycle. - Simple case

- CPU fetches an instruction from the main memory.

- Executes the instruction

- Called instruction cycle

- (fetch-execute-cycle)

28

Example Fetch-Execute-Cycle

- A two-stage cycle.

- Suppose we have 3 instruction I1, I2, I3.

- Without pipelining this will take 6 time units.

- With pipelining it will take only 4 time units.

- Why?

29

- Without pipelining

- Using pipelining

1 2 3 4 5 6

Fetch I1 I2 I3

Execute I1 I2 I3

1 2 3 4 5 6

Fetch I1 I2 I3

Execute I1 I2 I3

30

Six-Stage Instruction Cycle without pipelining

5 instructions A, B, C, D, E

1 2 3 4 5 6 7 . 12 ..

S1 A B

S2 A

S3 A

S4 A

S5 A

S6 A B

24 25 . 30

E

D E

31

Six-Stage Instruction Cycle with pipelining

5 instructions A, B, C, D, E

time stages 1 2 3 4 5 6 7 8 9 10

S1 A B C D E

S2 A B C D E

S3 A B C D E

S4 A B C D E

S5 A B C D E

S6 A B C D E

It takes 6 time unit to finish the instruction A,

and the other 4 instruction require 1 more time

unit each to finish there execution Therefore the

time required is 6 4 10

32

n-Stage Instruction Cycle

- Suppose we have m instruction

- Without pipelining

- nm

- With pipelining

- nm-1 time units.

- Explanation of the formulas

- The first instruction takes n time unit to be

executed completely. The other (m-1) instruction

will require one time unit for each one of them

to be executed completely. Therefore the time

requires to execute m instruction in n-stage

cycle is nm-1.

33

Disadvantage of pipelining()

- Data hazards

- Data hazards occur when data is modified.

- For example an operand is modified and read soon

after. Because instruction may not finished

writing to the operand, the second instruction

may use incorrect data. - Structural hazards

- Occurs when a part of the processors hardware is

needed by two or more instructions at the same

time - Control hazards

- occur when the processor is told to branch - IE,

if a certain condition is true, jump from one

part of the instruction stream to another one -

not necessarily the next one sequentially. In

such a case, the processor cannot tell in advance

whether it should process the next instruction

This can result in the processor doing unwanted

actions.

34

Exercise

- What are the difficulties of pipelining in a

conditional branch?

An unconditional branch is effectively just

one instruction in a straight sequence of

instructions so the pipeline can keep flowing.

With conditional branch, the processor

has to make a decision which path it has to take.

This can cause a problem if this decision depends

on the result of an instruction which has not yet

finished its path through the pipeline.

In this case the processor may proceed along

the wrong path and have to back up i.e. empty the

pipe and start again.