Abstractions in Verilog - PowerPoint PPT Presentation

Title:

Abstractions in Verilog

Description:

Continuous assignment statement. Can only assign wires, not registers. Assign is evaluated whenever the righthand side changes. Not allowed inside process blocks ... – PowerPoint PPT presentation

Number of Views:33

Avg rating:3.0/5.0

Title: Abstractions in Verilog

1

Abstractions in Verilog

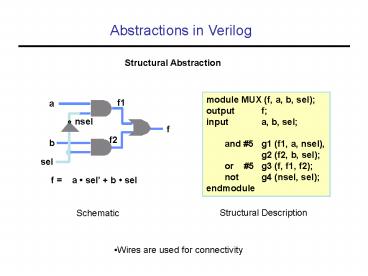

Structural Abstraction

module MUX (f, a, b, sel) output f input a, b,

sel and 5 g1 (f1, a, nsel), g2 (f2, b,

sel) or 5 g3 (f, f1, f2) not g4 (nsel,

sel) endmodule

Structural Description

Schematic

- Wires are used for connectivity

2

Behavioral Abstraction

module MUX (f, sel, b, c) output reg

f input sel, a, b always _at_ (sel or a or

b) begin if (sel 1) f

a else f b end endmodule

- Sequential statements

- Registers are assigned

- Word-level arithmetic can be used

3

Dataflow Abstraction

module MUX (f, sel, a, b) output reg

f input sel, a, b wire nsel, f1,

f2 assign nsel lt sel assign f1 lt a

nsel assign f2 lt b sel assign f lt f1

f2 endmodule

- Continuous assignment statement

- Can only assign wires, not registers

- Assign is evaluated whenever the righthand side

changes - Not allowed inside process blocks

4

State Machine Abstractions

- Moore machine - output is determined by state,

not input - Sequential design - contains flip-flops (2)

5

Behavioral Description, State Machine

- One block defines state transitions, one defines

outputs, one updates ffs

6

Moore Machine Structure

- Structural design - combinational logic

flip-flops - State update logic output logic

7

Moore Machine Structure