Probleem - PowerPoint PPT Presentation

1 / 1

Title:

Probleem

Description:

Title: No Slide Title Author: marcok Last modified by: p63 Created Date: 10/4/1999 7:22:29 AM Document presentation format: Custom Company: NIKHEF Other titles – PowerPoint PPT presentation

Number of Views:36

Avg rating:3.0/5.0

Title: Probleem

1

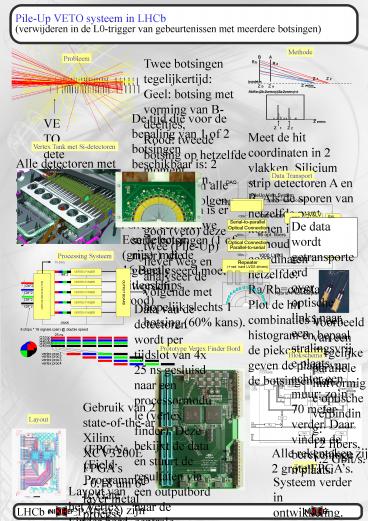

Pile-Up VETO systeem in LHCb (verwijderen in de

L0-trigger van gebeurtenissen met meerdere

botsingen)

Methode

Probleem

Twee botsingen tegelijkertijd Geel botsing met

vorming van B-deeltjes, Rood tweede botsing op

hetzelfde moment Moeilijk om alle sporen te

volgen, daarom gooi (veto) deze twee (Pile-Up)

liever weg en analyseer de volgende met hopelijk

slechts 1 botsing (60 kans).

De tijd die voor de bepaling van 1 of 2 botsingen

beschikbaar is 2 microseconden. Iedere 25

nanoseconden is er weer een nieuwe serie

botsingen (1 of meer) die geanalyseerd moet

worden

VETO detectoren

Meet de hit coordinaten in 2 vlakken Silicium

strip detectoren A en B. Als de sporen van

hetzelfde punt komen is de verhouding van de

coordinaten hetzelfde Ra/Rbconstant. Plot de

hit combinaties in een histogram en bepaal de

pieken deze geven de plaats van de botsingen aan.

Vertex Tank met Si-detectoren

Alle detectoren met daarbij de twee (achterste)

vlakken detectoren die gebruikt worden voor het

VETO systeem

Data Transport

De data wordt getransporteerd over optische

links naar een stralingsvrije plaats achter een

muur zon 70 meter verder. Daar vinden de

berekeningen plaats.

Een detector (grijs) met de 16 Beetle

uitleeschips (rood)

Processing Systeem

Data van de detectoren wordt per tijdslot van 4x

25 ns gesluisd naar een processormodule (vertex

finder). Deze bekijkt de data en stuurt de

resultaten via een outputbord naar de centrale

trigger.

Voorbeeld van een dergelijke parallele

lintvormige optische verbinding 12 fibers, 1.2

Gbit/s.

Prototype Vertex Finder Bord

Blokschema

- Gebruik van 2 state-of-the-art

- Xilinx XCV3200E FPGAs

- - 0.18 um 6-layer metal process

- 4.074.387 system gates

- - 804 I/O pins (344 LVDS pairs)

- 1156 pin Ball Grid Array!

Layout

(FPGAs (Field Programmable Gate Arrays) zijn

herprogrammeerbare chips waarbij uit simpele

gates logische eenheden worden opgebouwd.)

Alle rekentaken zijn opgesplitst over 2 grote

FPGAs.

Tot slot

Systeem verder in ontwikkeling. In 2007

ingebruikneming bij het LHCb experiment te Cern.

Layout van het Vertex Finder bord. Let op de vele

fijnmazige verbindingen rond de FPGAs