Status of DAQ - PowerPoint PPT Presentation

1 / 11

Title:

Status of DAQ

Description:

Title: Status of DAQ Subject: USCMS DAQ WBS 3.2 Author: Vivian O'Dell Last modified by: RL Created Date: 4/13/1998 5:33:42 PM Document presentation format – PowerPoint PPT presentation

Number of Views:97

Avg rating:3.0/5.0

Title: Status of DAQ

1

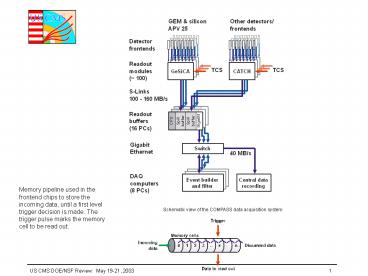

Memory pipeline used in the frontend chips to

store the incoming data, until a first level

trigger decision is made. The trigger pulse marks

the memory cell to be read out.

2

(No Transcript)

3

CMS DAQ Design

- Basic principle

- CMS DAQ is a number of functionally identical,

parallel, small DAQ systems - A 64x64 system is feasible today

4

CMS DAQ Design

- Basic principle

- CMS DAQ is a number of functionally identical,

parallel, small DAQ systems - A 64x64 system is feasible today

5

Detector readout to surface

6

Data to Surface SLink64/FRL

- SLink64 From FED to FRL

- Test pattern generator in sender card

- Test pattern verification in FRL

- FRL (Frontend Readout Link)

- Multiple firmware versions

- Spy functionality

- Event generator allows testing DAQ system without

operational FEDs

7

Event BuilderAll Commodity Backbone

- Commodity Computers commidity networking

(Myrinet/GigabitEthernet) - Myricoms LANaiX PCI-X, multiple links,

- LANai1XP since 1 April 2003/LANai2XP available

Oct 2003

Myricom Switches currently based on

Xbar16 Xbar32 under development First products

expected 2Q 2004

Measured bandwidth with two LANai1XP NICs serving

as PCI-X DMA engines Grand Champion 710 MB/s

per bus Intel Pluma 426 MB/s per

bus i.e. 1.4 GB/s aggregate dual bus

Grand Champion chipset by Serverworks

8

GB Ethernet TCP EVB 8x8

- XDAQ 8x8 EVB using gigabit ethernet

- Each BU builds 128 evts

- Fixed fragment sizes

- For fragment size gt 4 kB

- Thru /node 100 MB/s

- ie 80 utilization

- (Specification is 200 MB/s)

9

Myricom EVB 8x8

- Full XDAQ 8x8 EVB using Myricom (LanAI9)

- software overhead (e.g. EVM included)

- Each builder unit builds 128 evts

- Log-normal fragment size distribution

- At working point(16 kB)

- Thu/node 210 MB/s

- (Specification is 200 MB/s)

10

Filter Farm Test Stand

Dual 2.4 GHz Xeon with 2 GB memory, 40 GB disks

and dual on-board GE. Ran empty FU application

load BU output to a max at 100 MB/s (1 FU/node),

95 MB/s (2 FU/node) HLT application (small

event sample) CPU usage tests ongoing

11

Building names

Surface DAQ building

Underground Area