Urbana DAQ/Trig meeting - PowerPoint PPT Presentation

Title:

Urbana DAQ/Trig meeting

Description:

CLEO-III Trigger & DAQ Status Trigger Illinois (Cornell) DAQ OSU Caltech Cornell – PowerPoint PPT presentation

Number of Views:180

Avg rating:3.0/5.0

Title: Urbana DAQ/Trig meeting

1

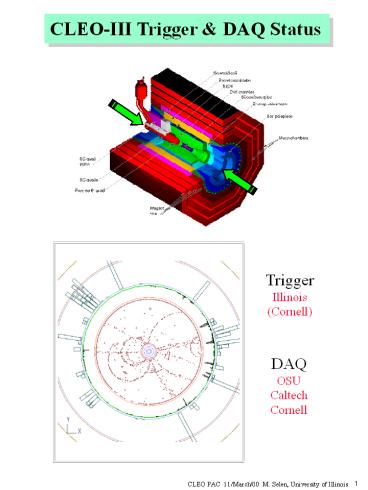

CLEO-III Trigger DAQ Status

Trigger Illinois (Cornell)

DAQ OSU Caltech Cornell

2

CLEO-III Trigger

At L 3 x 1033 this corresponds to 250 Hz.

Design CLEO-III trigger/DAQ for 1000 Hz max.

- Trigger Philosophy

- Make a sophisticated Level-1 trigger decision

(latency2.5ms) before invoking readout

dead-time. - Make trigger decision every 42ns (i.e. pipeline).

3

CLEO-III Trigger System Inventory

Mixer/Shaper Crates (24)

Drift Chamber Crates

Gates

CLEO

Mixer/Shaper Boards

Contr.

DR3 Pre-amps

G / CAL

Analog

TILE (8)

AXTR(16)

AXX(16)

DFC

DAQ

Flow control Gating

Barrel CC

QVME

TIM

TIM

Axial tracker

DM/CTL

DM/CTL

TILE (8)

Patch panel

Barrel CC

QVME

L1LUMI

STTR(12)

L1D

Stereo tracker

L1D

TILE (8)

TIM

Endcap CC

QVME

DM/CTL

Level 1 decision

AXPR

TCTL

CCGL

TPRO(4)

SURF

TPRO(2)

SURF

CC Digital

4

Trigger Hardware Example

Example (they all look similar)Level-1 Trigger

Decision Board

5

Common Trigger Board Structure

FPGA based Logic

Inputs

Outputs

DAQ/ VME

Circular Buffer

TDI TMS TCK

TDO

JTAG

6

Tracking Trigger (Axial Stereo)

7

Finding the Event Time

2 trackEvents

Trigger Bucket

8

CC Trigger

Energy sharing between boards can result in a

loss of efficiency

Threshold 500 MeV

9

Analog TILE Boards

10

Preliminary Peek at the CC Trigger Data

Barrel(Crate 1 Card 13)

Endcap(Crate 21 Card 16)

11

CC Tile Processor

1 m/s crate

?

?

12

Level 1 Decision

13

Writing Trigger Lines

- Generic Hadron Line, Barrel Timing

- SUBDESIGN line0(

- in117..0 INPUT

- out OUTPUT

- )

- Variable

- 1cblow SOFT

- 3tracks SOFT

- evtime SOFT

- Begin

- -- trigger bit mappings

- tr_time1..0 in1..0

- cb_time1..0 in3..2

- ce_time1..0 in5..4

- cc_time1..0 in7..6

14

Trigger Status

- All components (except STTR) boards installed and

functioning. - Used for collecting engineering run data

- Many bugs shaken out (all readout related)

- Some minor readout bugs remain, and will be

fixed. - Stereo tracking (STTR) boards will be installed

by the end of March. - 8 of 12 needed boards tested (and working) as of

today, the balance (4 spares) will be shipped

to LNS by the end of next week. - Majority of trigger groups effort turning to

software development. - Much already exists (readout, sparsification,

board debugging testing, expert online tools). - More user friendly (GUI) code being developed.

- Monte Carlo 90 finished.

15

CLEO III DAQ Architecture

16

Readout Controller

VME PowerPC VxWorks

Fastbus VME-Fastbus Interface (FRITZ)

17

CLEO III Slow Control Structure

Level 3

Event Builder

Crates

Run Control

Gas

CORBA

HV

Database

Beam

User Console (Java)

Magnet

18

DAQ Status

- All key components installed and functioning.

- True for both Data Path Slow Control

- 32 PowerPC crate-based CPUs used

simultaneously during engineering run! - 8 VME crates reading out the 230000 RICH

channels. - 3 VME crates reading out the trigger system.

- 2 VME crates reading out the Silicon Vertex

System. - 4 FASTBUS crates reading out the CC via FRITZ

- 8 FASTBUS crates reading out the DR via FRITZ.

- 7 PowerPCs performed slow control tasks.

- Event Builder worked as expected

- This is a big deal !

- The system will grow slightly for complete

CLEO-III data-taking in April - 1 additional VME crate reading out the stereo

trigger. - 3 additional VME crates for reading out the

silicon. - Stability and User Friendliness improving every

day.