MOCVD - PowerPoint PPT Presentation

1 / 31

Title:

MOCVD

Description:

MOCVD Growths are performed at room pressure or low pressure (10 mtorr-100 torr) Wafers may rotate or be placed at a slant to the direction of gas flow – PowerPoint PPT presentation

Number of Views:904

Avg rating:5.0/5.0

Title: MOCVD

1

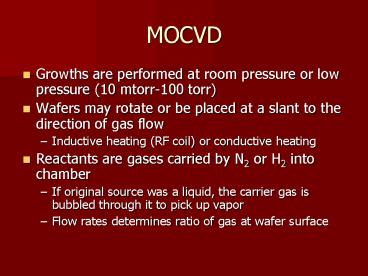

MOCVD

- Growths are performed at room pressure or low

pressure (10 mtorr-100 torr) - Wafers may rotate or be placed at a slant to the

direction of gas flow - Inductive heating (RF coil) or conductive heating

- Reactants are gases carried by N2 or H2 into

chamber - If original source was a liquid, the carrier gas

is bubbled through it to pick up vapor - Flow rates determines ratio of gas at wafer

surface

2

Schematic of MOCVD System

http//nsr.mij.mrs.org/1/24/figure1.gif

3

http//www.semiconductor-today.com/news_items/2008

/FEB/VEECOe450.jpg

4

Advantages

- Less expensive to operate

- Growth rates are fast

- Gas sources are inexpensive

- Easy to scale up to multiple wafers

5

Disadvantages

- Gas sources pose a potential health and safety

hazard - A number are pyrophoric and AsH3 and PH3 are

highly toxic - Difficult to grow hyperabrupt layers

- Residual gases in chamber

- Higher background impurity concentrations in

grown layers

6

Misfit Dislocations

- Occur when the difference between the lattice

constant of the substrate and the epitaxial

layers is larger than the critical thickness.

http//www.iue.tuwien.ac.at/phd/smirnov/node68.htm

l

7

Critical Thickness, tC

- where

- b is the magnitude of the lattice distortion

caused by a dislocation (Burger vector) - f is the mismatch between the lattice constants

of film and the substrate - n is Poissons ratio (transverse strain divided

by the axial strain).

8

Key Inventions

- Three discoveries made integrated circuits

possible - Invention of the transistor(1949 by Brattain,

Bardeen, and Schockley Nobel prize 1972) - Development of planar transistor technology(1959

by Bob Noyce and Jean Hoerni Noyce was a founder

of Intel) - Invention of integrated circuit(1959 by Kilby

Nobel prize 2000)

9

The First Transistor

- The first transistor, a point contact pnp Ge

device, was invented in 1947 by John Bardeen,

Walter Brattain, and William Shockley. They

received the Nobel Prize in physics in 1956.

10

The first integrated circuit

- The first integrated circuit was invented by Jack

Kilby of TI. He received the Nobel Prize in 2000.

11

Levels of Integrated Circuits

- Small Scale Integration (SSI)

- 1-10 transistors

- Medium Scale Integration (MSI)

- up to 100 transistors

- Large Scale Integration (LSI)

- up to 10,000 transistors

- Very Large Scale Integration (VLSI)

- millions of transistors

- Ultra Large Scale Integration

- Wafer Scale Integration

- System on a Chip (SOC)

- System in a Package (SiP)

- 3D IC

12

Increase in Complexity of Chips

13

Moores Law

- Gordon Moore observed (1965) that the number of

transistors on a Si chip was doubling every year.

Later, revised this to every 18 months. - This cannot continue forever when components

reach size of atoms, the physics changes. - Currently, there is no known solution.

14

(No Transcript)

15

Historical Trends of Minimum Feature Size

Minimum Feature Size 13 reduction each year

recently closer to 10.

16

Projections from 1997 Roadmap

- The fundamental assumption is that Si will be the

material of choice and that Moores law will

apply until 2012

17

Scaling as a Function of Cycle Time

S is the minimum feature size T is the cycle

time CARR is the Compound Annual Reduction

Rate On average, the minimum feature size

decreases by 10-13/year. Currently at 45 or 32

nm node

18

Where are we today?

19

(No Transcript)

20

(No Transcript)

21

(No Transcript)

22

Semiconductor Trends

- Overall chip size has been increasing by 16/year

over past 35 years - Recently 6.3/year for microprocessors and

12/year for DRAM - Major limitation is the number of pads that can

be placed on the chip to get signals in and out - Trends are now projected by the SIA national

Technology Roadmap for Semiconductors - Current version is called International

Technology Roadmap for Semiconductors

23

(No Transcript)

24

Cost of Designing a Chip

- The cost of designing a chip has increased with

the complexity of the chip. - Initially, the cost seemed to follows Moores

lawthe cost doubled every time the complexity

doubled. - The controlling factor was the development of CAD

and modeling software.

25

Cleanrooms

Federal Standard TC 209 ISO

1

2

1 3

10 4

100 5

1,000 6

10,000 7

100,000 8

9

26

ISO FED STD 209 0.1 µm 0.2 µm 0.3 µm 0.5 µm 5.0 µm

CLASS 3 1 1000 / 35 35 / 1

CLASS 4 10 10,000 / 345 75 30 352 / 10 0

CLASS 5 100 100,000 / 3,450 750 300 3520 / 100 0

CLASS 6 1,000 1,000,000 / 34,500 N/A N/A 35,200 / 1,000 7

CLASS 7 10,000 345,000 N/A N/A 352,000 / 10,000 70

CLASS 8 100,000 3,450,00 N/A N/A 3,520,000 / 100,000 700

ISO 14644-1 (per cubic meter)Fed Std. 209 E USA

(per cubic foot)ISO standard requires results to

be shown in cubic meters (1 cubic meter 35.314

cubic feet)

27

Room Classifications Class Class Class Class Class Class

Classification System

ISO 14644-1 Class 3 Class 4 Class 5 Class 6 Class 7 Class 8

Federal Standard 209E 1 10 100 1,000 10,000 100,000

EU GGMP - - A/B - C D

Air Changes per hour 360-540 300-540 240-480 150-240 60-90 5-48

28

HEPA Filters

- High Efficiency Particulate Air (HEPA) filters

are 99.99 efficient in removing particles 0.3

micron and larger. HEPA filters utilize glass

fiber rolled into a paper-like material. This

material is pleated to increase the fiber surface

area and bonded, or potted, into a frame. Hot

melt is used to hold the pleats far enough apart

to allow air to flow between them.

29

Positive Pressurized Rooms

Air returns are built into the room usually

integrated into the chase. Chases are the

separate areas along side of the cleanroom that

contain pumps, gas cylinders, and other needed

(but dirty) materials and equipment.

http//terrauniversal.com/products/cleanrooms/phar

mclroom.php

30

First Line of Protection Bunny Suits

www.intel.com

31

Similar bunny suit to what is worn up in the 6th

floor Whittemore cleanroom and other Class

100-10,000 cleanrooms. Missing elements are the

face shield and safety eyeglasses.