Hardware Review - PowerPoint PPT Presentation

1 / 55

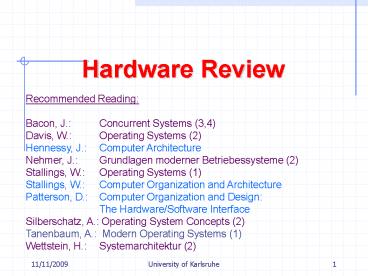

Title: Hardware Review

1

Hardware Review

Recommended Reading Bacon, J.

Concurrent Systems (3,4) Davis, W. Operating

Systems (2) Hennessy, J. Computer

Architecture Nehmer, J. Grundlagen moderner

Betriebessysteme (2) Stallings, W. Operating

Systems (1) Stallings, W. Computer Organization

and Architecture Patterson, D. Computer

Organization and Design

The Hardware/Software Interface Silberschatz,

A. Operating System Concepts (2) Tanenbaum, A.

Modern Operating Systems (1) Wettstein, H.

Systemarchitektur (2)

2

Hardware Overview

Overview Memory Hierarchy Principle of

Locality Caching Processor Exceptio

n/Interrupt I/O-Interfaces

3

Motivation

Why Hardware Review?

- OS controls hardware

- Hardware controls OS

- Hardware induces parallelism, OS has to deal

with - Parts of an OS kernel are hardware dependent

- Real-time applications need specific hardware

support

4

Hardware Overview

Flynns System Classification

5

Hardware Overview

Hardware Base for Concurrent Systems

Increasing concurrency

Uniprocessor

6

Hardware Overview

Concrete Hardware Architectures

- Single Processor System

- Multi Processor System

- Local Area System (LAN)

7

Hardware Overview

Single Processor System

Processor 1

disk

L1 cache

printer

...

L2 cache

controller

controller

system bus

main memory

8

Hardware Overview

Multi Processor System

Processor 1

disk

L1 cache

printer

...

L2 cache

controller

controller

system bus

main memory

9

Hardware Overview

Local Area System

Diskless Client

Client

10

Hardware Overview

Basic Components

- Memory hierarchy main memory (RAM), caches (L1,

L2) - Processors (CPUs)

- Interconnection (e.g. buses)

- communication among processors, memory, and I/O

modules - I/O controllers, channels, I/O-processors

- hardware (with registers called I/O ports)

controlling devices and - transfering data between devices, consisting of

an extra CPU memory, e.g. IDE controller,

keyboard controller, network card, DMA, Timer /

real-time clock, UART (RS232C, V.24, modem) - Peripheral Devices

- disk, printer, keyboard, mouse, monitor, speaker,

microphone, ...

11

Hardware Overview

Basic Components

Memory Address Register

Memory Buffer Register

I/O-Address Register

I/O-Buffer Register

12

Hardware Overview

Specific CPU Registers

- MAR - Memory Address Register

- address for next read or write

- MBR - Memory Buffer Register

- data to be written into memory

- receives data read from memory

- I/OAR - I/O Address

- specifies a particular I/O device

- I/OBR - I/O Buffer

- exchange of data between an I/O module and the

processor

13

Hardware Overview

Memory Hierarchy

Register

L1 Cache

L2 Cache

L3 Cache

Main Memory

Disk Memory

Archive Memory

Note Parts of main memory may be used as a disk

cache

14

Hardware Overview

Memory Characteristics

Remark You should be able to fill this table

with up-to-date values!!!

15

Hardware Overview

Why is memory hierarchy useful?

M1 (fast, small, expensive)

Currently executing program

M2 (slow, large, cheap)

16

Hardware Overview

Why is memory hierarchy useful?

M1 (fast, small, expensive)

Problem How to map this large entity into that

small cache?

Currently executing program

M2 (slow, large, cheap)

17

Hardware Overview

Why is memory hierarchy useful? ? Principle

of Locality!!

M1 (fast, small, expensive)

Solution mapping piece by piece

Currently executing program

M2 (slow, large, cheap)

18

Hardware Overview

Spatial Locality

- near addresses are accessed next

- instructions ahead

- local variables of a procedure

- next elements of an array / a structure

Locality in Time

- some addresses are used frequently, or in bursts

- instructions inside a loop

- frequently called procedures

- important variables

- top of the stack

19

Hardware Overview

Simplified Performance Analysis of a 2-Level

Memory (write-through cache)

Tavr Tcache MissRate Tram

Tcache 1 ns Example Tram

400 ns MissRate 5 Tavr 21 ns

2 Tavr 9 ns

20

Hardware Overview

Simplified Analysis of a 3-Level Memory (L1 and

L2 Cache) (write-through caches, inclusion

property assumed)

Tavr TL1 MissL1 TL2 MissL2 Tram

TL1 1 ns MissL1 5 3

Example TL2 20 ns MissL2

0.5 0.3 Tram 400 ns Tavr 4

ns 2.8 ns

21

Hardware Overview

Note These are 1999 numbers

Cache Memory Design Parameters

- Size 8K - 265K (L1), 256K - 8M (L2)

- Block Size (32 128 B)

- Access Time (1 10 ns)

- Mapping (full associative, n-associative,

- direct-mapped)

- Replacement (LRU, FIFO,...)

- Write Policy (write through, write back)

Attention In most systems caches are invisible

to applications. However, cache reservation for

specific applications (e.g. in real-time systems)

may be useful.

22

Hardware Overview

Cache Memory Architecture

23

Hardware Overview

Cache Memory Design

- Cache size

- even small caches have a significant impact on

performance - Cache Line size (Block size)

- unit of data exchanged between cache and main

memory - hit means the information was found in the cache

- larger block size ? hit rate

- until probability of using newly fetched data

becomes less - than the probability of reusing data that has

been moved - out of cache

24

Hardware Overview

Cache Memory Design

- Mapping function

- determines which cache location the block will

occupy - Replacement algorithm

- determines which block to replace

- Least-Recently-Used (LRU) algorithm

25

Hardware Overview

Cache Memory Design

- Write policy determines

- when a block of cache is written to main memory

- can occur every time a cache line is updated

- (write-through policy)

- can occur only when the cache line has to be

replaced - (write-back policy )

- Minimizes memory operation

- Leaves memory in an obsolete state

26

Hardware Overview

Buffering/copying within a write-back memory

hierarchy

Assumption Original of data item within Memory

Level n

Level 1

(n-1)th Copy

Level n-1

1. Copy

Level n

Original

Observation Before accessing the first time,

this data item has to be copied

several times

27

Hardware Overview

Buffering/copying within a write-back memory

hierarchy

Assumption Original of data item within Memory

Level n

Level 1

Modification on this copy

Level n-1

Old 1. Copy

Level n

Old Original

Observation Modifying a data item on the

uppermost memory level affects data

consistency.

28

Hardware Overview

Buffering/copying within a write-back memory

hierarchy

Assumption Original of data item within Memory

Level n

Level 1

Write back dirty cache line

Level n-1

New 1. Copy

Level n

Old Original

Observation Modifying a data item on the

uppermost memory level affects data

consistency. Propagation of modified data

to lower levels can be done at once or

stepwise.

29

Hardware Overview

Buffering/copying within a write-back memory

hierarchy

Assumption Original of data item within Memory

Level n

Level 1

Load another data item.

Level n-1

New 1.Copy

Level n

Old Original

30

Hardware Overview

Branching Memory Hierarchy

Questions Why 2 archive memories? Additional

levels with similar branches? Additional

consistency problems?

31

Hardware Overview

Study for Yourselves

J. Liedtke Caches Versus Object

Allocation, In 5th IEEE International Workshop

on Object-Orientation in Operating Systems

(IWOOOS), Seattle, WA, October 1996. J.

Liedtke Potential Dependencies between caches,

tlbs, and memory managem,ent schemes,

Arbeitspapiere der GMD, No. 962, 1995

Remark Potential topics within the Proseminar

Linux Internals You should know both papers by

heart!!!

32

Hardware Overview

Functions of a simplified Processor

- Fetching instruction

- Executing instruction

- Moving data

- Manipulating data

33

Hardware Overview

Simplified Processors offer

- Instruction Set

- General and Special Registers

- 2 Hardware Modes

34

Hardware Overview

Simplified Processors offers

- Instruction Set

- General and Special Registers

- 2 Hardware Modes

- Privileged Instructions

- Non-Privileged Instructions

Give some examples! Why do we need privileged

instructions?

35

Hardware Overview

Simplified Processors offers

- Instruction Set

- General and Special Registers

- 2 Hardware Modes

Instruction Pointer Instruction

Register Processor Status Word ...

- control / status registers

- user-visible registers

- data registers

- address registers

- segment registers

- stack pointer

- condition codes / flags

Give some examples! Why do we need special

registers?

36

Hardware Overview

Simplified Processors offers

- Instruction Set

- General and Special Registers

- 2 Hardware Modes

- Kernel Mode

- User Mode

Why do we need both modes?

37

Hardware Overview

The Basic Instruction Cycle

CPU fetches the next instruction (with operands)

from memory. CPU executes the instruction Instruct

ion Pointer (IP) holds address of the instruction

to be fetched next, automatically incremented

after each fetch

38

Hardware Overview

Exception

Interrupt

- synchronous CPU event

- origin current instruction(s)

- erroneous exceptions

- invalid pointer

- division by 0

- gt typically program is aborted

- non-erroneous exceptions

- page fault

- breakpoint

- gt typically handled by OS, transparent to user

program

- asynchronous event

- origin I/O device, timer

- unrelated to instruction stream

- Most interrupts are caused by I/O-completion,

etc. (discussed later) - Failures cause a few interrupts (paper jam,

device malfunction, ...)

39

Hardware Overview

Exception

Interrupt

- synchronous CPU event

- origin current instruction(s)

- erroneous exceptions

- invalid pointer

- division by 0

- gt typically program is aborted

- non-erroneous exceptions

- page fault

- breakpoint

- gt typically handled by OS, transparent to user

program

- asynchronous event

- origin I/O device, timer

- unrelated to instruction stream

- Most interrupts are caused by I/O-completion,

etc. (discussed later) - Failures cause a few interrupts (paper jam,

device malfunction, ...)

Dont mix up exceptions and interrupts

40

Hardware Overview

CPU waits for I/O to complete

A WRITE transfers control to the printer driver

(I/O program). Printer driver prepares I/O module

for printing (4). CPU has to WAIT for the print-

operation to complete. Printer driver finishes in

(5) reporting status of I/O operation.

41

Hardware Overview

Interrupts

- Many computers permit I/O modules

- to INTERRUPT an activity on the CPU

- For this the I/O module just asserts

- an interrupt request line on the control bus

- Then the CPU transfers control to an

- Interrupt Handler (normally part of the OS)

- The CPU can prevent to be interrupted,

- by masking out or disabling interrupts

42

Hardware Overview

Instruction Cycle with Interrupts

Interrupt disabled

Check for Interrupts Y Raise Interrupt

Fetch Next Instruction

Execute Instruction

Start

Interrupt enabled

Halt

43

Hardware Overview

Interrupt Handler

- program that determines type of the interrupt

and - performs whatever actions are needed

- an interrupt interrupts the currently executing

program - and invokes the interrupt handler

- interrupt handler must return to the interrupted

program - so that it can be resumed from the point of

interruption - point of interruption can occur anywhere, so the

handler - must save the state of the interrupted program

- (IP, PSW, registers ...) and restore it upon

return

44

Hardware Overview

Interrupt Processing

45

Hardware Overview

Interrupts improving CPU usage

I/O program prepares I/O module, issues I/O

command (to a printer) I/O program branches to

the user program, user code gets executed

during I/O operation (e.g. printing) ? no

waiting User program gets interrupted (x) when

I/O operation is done and branches to interrupt

handler to examine status of I/O

module Execution of user code resumes

46

Hardware Overview

Multiple Interrupts Strict Sequential Order

Remark Disable all interrupts during interrupt

processing. Interrupts remain pending until the

processor enables interrupts After interrupt

handler has completed processor checks for

further pending interrupts

47

Hardware Overview

Low priority interrupt

Multiple Interrupts Priorities

High priority interrupt

Low-priority interrupt handling no longer delays

high-priority interrupt processing. High-priority

interrupt cause a low-priority interrupt handler

to be interrupted.

Example When input-data arrive from the

network, it needs to be consumed quickly to make

room for further incoming data.

48

Hardware Overview

I/O Module Structure

Data to/from system bus are buffered in data

register(s) Status/Control register(s) holds

current status information current control

information from I/O logic interacts with CPU

via control bus Contains logic specific to the

interface of each device

49

Hardware Overview

I/O-Interface Techniques

- Programmed I/O (polling)

- Interrupt Driven I/O

- Direct Memory Access (DMA)

Well discuss these techniques in detail in the

tutorials!

50

Hardware Overview

Programmed I/O

I/O module performs the action, on behalf of the

processor I/O module does not interrupt the CPU

when I/O is done Processor is kept busy checking

status of I/O module

51

Hardware Overview

Interrupt-Driven I/O

Processor is interrupted when I/O module is

ready to exchange data, e.g. if requested

operation finished. Processor is free to do

other work in the meantime, no busy

waiting. Well-suited for medium-grained

event. Bad for frequent fine-grain events gt

high CPU costs per interrupt. - Interrupt per

incoming network packet might work - Interrupt

per byte is far too expensive.

52

Hardware Overview

Direct Memory Access

CPU issues request to a DMA module (separate

module or incorporated into I/O module) DMA

module transfers a block of data directly

to/from memory, not through CPU) Interrupt is

sent when DMA is complete. CPU is only involved

at the beginning and at the end of the transfer,

it is free to perform other jobs during data

transfer. However note DMA may put heavy load

on memory bus gt problem of cycle stealing

53

Hardware Overview

Only Physical Addressing of Main Memory

To access (either read or write) the desired

buffer some device controllers (e.g. a DMA) can

address only physical addresses.

Example Controller has to transfer a

block to main memory

What may happen?

54

Hardware Overview

Only Physical Addressing of Main Memory

To access (either read or write) the desired

buffer some device controllers (e.g. a DMA) can

address only physical addresses.

Main Memory

Main Memory

Buffer of

move (0815), 4096

4096

0815

Controller

Due to I/O problems there is a transfer delay, gt

meanwhile frame 4096 has been used for some

other activity because of paging or

segmentation requirements.

How to solve this problem?

55

Hardware Overview

Only Physical Addressing of Main Memory

To access (either read or write) the desired

buffer some device controllers (e.g. a DMA) can

address only physical addresses.

Main Memory

Buffer of

move (0815), 4096

4096

0815

Controller

Pinning this frame, i.e. as long as DMA

transfer is not yet completed, this frame cannot

be used otherwise!