Overall ECAL schedule - PowerPoint PPT Presentation

Title:

Overall ECAL schedule

Description:

Design now frozen after two iterations. Production to start any day, finish by end of Dec ... Testing and firmware development. 1 October 2003. Paul Dauncey. 5 ... – PowerPoint PPT presentation

Number of Views:18

Avg rating:3.0/5.0

Title: Overall ECAL schedule

1

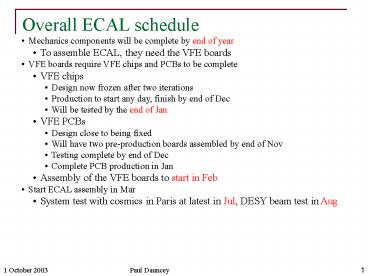

Overall ECAL schedule

- Mechanics components will be complete by end of

year - To assemble ECAL, they need the VFE boards

- VFE boards require VFE chips and PCBs to be

complete - VFE chips

- Design now frozen after two iterations

- Production to start any day, finish by end of Dec

- Will be tested by the end of Jan

- VFE PCBs

- Design close to being fixed

- Will have two pre-production boards assembled by

end of Nov - Testing complete by end of Dec

- Complete PCB production in Jan

- Assembly of the VFE boards to start in Feb

- Start ECAL assembly in Mar

- System test with cosmics in Paris at latest in

Jul, DESY beam test in Aug

2

BUT

- Considered essential to have a VFE board/readout

board test before VFE PCB production - N.B. Too late to test prototype/prototype before

their pre-production - Will be preproduction/prototype so hard to argue

they need to change if problems found - Schedule would have VFE PCBs released for

production in Jan - To not cause a delay to this (and hence whole

ECAL), would need to do VFE/readout test in Dec - Possible but not likely given prototype readout

boards arriving in early Nov - We said at Paris we would aim for asap but Jan at

latest - This gives one month delay to whole ECAL assembly

schedule - But still aim for DESY beam test in Aug

- Despite delays of 3 months to other parts of

the project, we are the critical path for the

whole ECAL

3

Longer term

- Working backwards from the end

- DESY beam test in Aug and system test in Jul mean

we need (minimum of) Jun for testing after board

production - One month is short for board production tests,

crate test, testing all final firmware, system

tests/commissioning, etc. - Production fabrication and assembly must finish

by end of May - One month for this should be reasonable

- Production layout must finish by end of Apr

- Assuming changes are needed

- Redesign must finish by end of Mar

- This assumes one month for layout (!) after

changes finalised

4

Testing and firmware development

- We therefore have three deadlines for

firmware/testing - End of Dec be ready for VFE/readout test

- Presumably using Chipscope, not final firmware

- End of Mar identify all changes to board

- Finalise hardware changes in time for re-layout

(if needed) - End of Jun be ready for system test

- Need final, fully-functional versions of all

firmware - All three are critical path for whole ECAL

project - The final one is self-explanatory lets consider

the other two in more detail

5

VFE/readout tests by end Dec

- Four sets of tests which we need to do

- Run the basic readout sequence and see data out

of ADCs - Trigger/SH can be randomly timed dont need

320MHz fine adjust - Measure the noise in this configuration

- Need to take 100s of events and record ADC

values of all 216 chns - Need to tune timing parameters of readout

sequence turn-around for changing them 30 mins?

Is this too long for sensible testing? - Use the DACs to see signals above the pedestals

and get a (non-)linearity measurement - Need DACs, calibration pulse and to have fine

320MHz adjust of SH - Use the Paris cosmic testbench to see cosmic

signals - Need external trigger to fire FE sequence need

BE trigger logic to veto further triggers or can

use Chipscope? - This implies the tests will be done in Paris

only one fully-loaded pre-prototype VFE

PCB anyway so unlikely to let us borrow it

6

VFE/readout tests (cont)

The parts of the FE which need to be working for

tests 1 2 3 4

7

Board changes/verification by end Mar

- Connectivity/layout errors

- JTAG tests will find these quickly

- Choice of FE FPGA component size/speed

- Need semi-final versions of FE code to be sure

what would be enough? - Too much ADC noise

- Will be known at time of VFE tests

- Cause and solution may be harder to determine

- Missing VME functionality

- E.g. those not used (tested?) by CMS DMA and VME

interrupts - Miscellaneous features or missing functionality

- How bad would these have to be for us to fix them

if we find them? - VFE required changes

- Should be found during VFE tests

- To be really sure, should have full system

working what is enough?