GigE Interface Board - PowerPoint PPT Presentation

1 / 23

Title:

GigE Interface Board

Description:

The final block in the message is an End-of-Frame [EOF] ... Free. MAC chip $ 150. PCB Board $ 100-300. FPGA. Brief Overview. Designing an GigE interface board. ... – PowerPoint PPT presentation

Number of Views:53

Avg rating:3.0/5.0

Title: GigE Interface Board

1

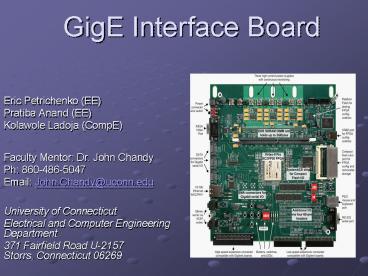

GigE Interface Board

- Eric Petrichenko (EE)

- Pratiba Anand (EE)

- Kolawole Ladoja (CompE)

- Faculty Mentor Dr. John Chandy

- Ph 860-486-5047

- Email John.Chandy_at_uconn.edu University of

Connecticut - Electrical and Computer Engineering Department

- 371 Fairfield Road U-2157 Storrs, Connecticut

06269

2

Background

- Many advances in computer technology recently but

access time have not kept up - Great need for high-performance storage systems

- Therefore a storage network is being built

- Using a Benes Network

- Is a type of multistage switching network

Figure 1. Benes Network

3

Background Continued

- The switching network will be using the XUP2VP

board from Xilinx/Diligent at the nodes - The XUP2VP has an on-board Ethernet connection

but it only runs at 10/100 Mbps - We need the Ethernet connection to run at 1000

Mbps

4

Introduction

- Our project

- To create a board that fills in the hole from

SATA to GigEthernet (will be explained in more

detail later) - Chose to use SATA from the board because of the

high speed transfer rate

Figure 2. Project Outline

5

Specifications

6

SATA (Serial Advanced Technology Attachment)

- SATA is a computer bus technology primarily to

transfer of data to and from a hard disk. - Replacement for the Parallel ATA physical storage

interface. - Because faster speed

7

SATA-Xilinx (XUP V2-Pro)

- Out of 8 Rocket I/O Channels three are SATA

channels - The SATA channels are split into two interface

formats, two HOST ports and a TARGET port. - The SATA data rate upto 2.5 Gb/s

Figure 2. SATA Part of the Board

8

SATA-Protocol

- The SATA Frame structure used between Host and

Device is shown in the figure. - The SATA frame begins with a Start-of-frame

SOF. - The SOF is followed by the Frame Information

Structure FIS. - Then the Cyclic Redundancy Code CRC is placed

in the frame. - The final block in the message is an End-of-Frame

EOF.

Figure 3. SATA Bus Protocol Frame

9

Ethernet

- Ethernet is comprised of MAC and PHY

- Diagram below shows the flow from SATA to Ethernet

Figure 4. Detailed diagram of GigEthernet

10

What is the Media Access Control (MAC) Sub Layer?

- One of two sublayers that make up the Data Link

Layer of the OSI model - Controls how a computer on the network gains

access to the data and permission to transmit it.

Figure 5. Flow Chart of OSI.

11

MAC Sub Layer

- Acts as an interface between the Logical Link

Control sublayer and the network's physical layer

- Physical Layer transmits raw bits rather than

packets - The physical layer determines the bit rate

(connection speed) - MAC layer is primarily concerned with the control

of access to the physical transmission medium.

Figure 6. IEE802 Diagram.

12

Purpose of MAC

- Moves data packets to and from one Network

Interface Card (Xilinx XUP-V2Pro) to another.

Figure 7. MAC encapsulation of a packet of data

13

Specific Chip Options

- Intel 82547EI Gigabit Ethernet Controller Intel

MAC with integrated PHY. Uses a CSA bus protocol

to get data onto the chip. Therefore an

interface between SATA and CSA would be necessary

for this chip. - PMC 3386 Does not contain an integrated PHY. To

connect with a PHY it uses the industry standard

GMII protocol. Contains dual GigE MACs which is

beneficial because each board is connected to 2

Ethernet lines. - Build MAC Our Self Use open core Gigabit MAC

and put on the FPGA along with our SATA logic.

14

Final Decision of MAC

- Create the MAC ourself

- Use VHDL code from www.opencores.org

- Edit the code to be compatible with our specific

setup - Benefits

- More Flexibility

- Free

- No constraints

- Can change code whenever

- Enables upgrading and maintanence

15

PHY Chip

- The www.opencores.org MAC needs an external PHY

Chip - PHY Chip must have GMII Protocol to be compatible

with the MAC Code - Choices

- Marvell Alaska has many single-port transceivers

with GMII Protocols that are 1000 Base - Depending on price and availability we will make

a decision

16

Glue Logic

- Purpose

- The purpose of the glue logic is to accepts data

packets from the MAC that connects to the gigabit

Ethernet and make it compatible with SATA which

is used by the XUP 2V - Pro board and vice versa

(MAC ? SATA). - Ethernet SATA or Vice versa

- Implementation

- Discrete Logic? No

- FPGA? Yes

- Why?

17

Glue Logic

Team 8 will be using an FPGA to implement the

glue logic because of the limitations that

discrete logic possesses.

18

Glue Logic

- There are three major concerns

- Data format

- Data needs to be made compatible from one format

into the another

- Error checking

- Corrupted or invalid data is of no use to the

user. - Glue Logic will have to check the data packets

from SATA for errors. Also, it will have to

provide some kind of data packet information

(CRC) so that the XUP 2V - Pro board can check if

the data packet has been corrupted of not.

19

Glue Logic

- Data transfer Rates

- SATA Less than 2.5 GBits/s

- Ethernet steady rate of 1Gbits/s

- Clock rate of 1.25 GHz

- SATA transfers data serially while Ethernet

transfers data in parallel. - How do we plan to solve this problem? With the

use of SERDES (serializer / deserializer),

clocks, and buffers

20

Glue Logic Block Diagram

Figure 8. Glue Logic Block Diagram

21

Timeline

- Spring 2007

- Complete design in VHDL code

- Complete testing of the design

- Send out specs of PCB for manufacturing

- Implementing and testing the Final Product

- Fall 2006

- Preliminary design

- Implementation in VHDL code

- Ordering supplying

22

Budget

23

Brief Overview

- Designing an GigE interface board.

- Purpose and motivation

- SATA

- MAC and PHY

- GLUE Logic

ANY QUESTIONS ????????