Driver 1: Single Chip Network Element - PowerPoint PPT Presentation

1 / 10

Title:

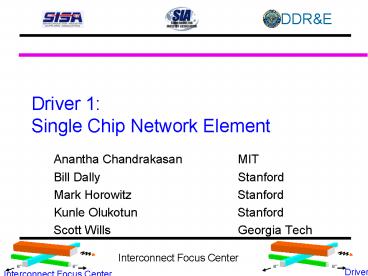

Driver 1: Single Chip Network Element

Description:

Scott Wills Georgia Tech. Driver1. Interconnect Focus Center. The Bandwidth Bottleneck ... Explosion in bandwidth use will cause bandwidth bottlenecks ... – PowerPoint PPT presentation

Number of Views:20

Avg rating:3.0/5.0

Title: Driver 1: Single Chip Network Element

1

Driver 1 Single Chip Network Element

- Anantha Chandrakasan MIT

- Bill Dally Stanford

- Mark Horowitz Stanford

- Kunle Olukotun Stanford

- Scott Wills Georgia Tech

Interconnect Focus Center

e

e

e

e

2

The Bandwidth Bottleneck

- Internet traffic increasing at 2.5x per year

- Twice rate of Moores law

- 1 Tb in 2001

- 4000 Tb in 2010

- Where is the bottleneck?

- Web server

- First mile

- Backbone networks

- Last mile

Web Data Center

Router

First mile

Internet Backbone

Access

Last mile

3

Router Architecture

Routing Processor

Output Ports

Input Ports

Switching Fabric

Output Links 512 x 40 Gb

Input Links 512 x 40 Gb

- Challenges

- Power

- Redundancy

- I/O Bandwidth

4

Transaction Server

- Servers

- Web server (static, dynamic, video)

- Database server (OLTP)

- Characteristics

- Lots of threads

- Lots of sharing between threads

- Huge memory footprint

- Throughput is more important than latency

- Implications

- Throw out ILP

- Reduce use of caches

- High memory and disk BW

5

2010 Single Chip Network Element

6

Architecture Research I

- Application mapping

- discover locality in application that can be

exploited statically and dynamically - map to a modular, wire-efficient VLSI

architecture with power considerations - Network Router

- Challenge map classification, forwarding, QoS

- Must keep up with line rates (40 Tb/s)

- Network Server

- Threads naturally map to multiprocessors

- Need shared memory abstraction

- Caches vs. latency tolerance?

7

Architecture Research II

- On-chip network

- Flow control for static and dynamic traffic

- New interconnect topologies optimized for a

single chip - Processor

- Interconnect oriented architecture

- Distributed register files

- Distributed instruction issue

- Interconnect modeling and simulation

- Efficient connections to on-chip network

8

Circuits Research

- Efficient Signaling Circuits

- Increasing signal velocity with overdrive

- Reducing power with low-swing signaling

- Reducing energy with coding

- RF vs. optical vs. electrical for on-chip

networks - Clock distribution and Synchronization

- Clock networks dissipate 25-50 of chip power

- Distributing low skew clocks is challenging

- Solutions distributed clocking, active skew

management, optics

9

Optics and 3-D Semiconductor Research

- Integrated Optics required for Router application

- Reduces power

- Increases bandwidth

- 40 Gb/s link requires

- Advances in optical transmitters, receivers and

packaging - Power-efficient interface circuits

- Improve state of CMOS I/O and clock circuit

design - Gateway to on-chip networks

- Use of 3-D semiconductor Technology

- Optimize architecture for reduced wire lengths of

3-D technology - Build storage, buffers, repeaters and switches

close to layers of network interconnect

10

Conclusions

- Explosion in bandwidth use will cause bandwidth

bottlenecks - Single-chip network element with optical I/O can

break these bottlenecks - Success will require a combination of

architecture, circuits and technology research