Subcircuits - PowerPoint PPT Presentation

1 / 83

Title:

Subcircuits

Description:

Once M2 turns on at t3, all charge on C1 is transferred to C2 ... Generally, gm 10 gmbs 100 gds. If VBS=0, Voltage Division. Equating iD1 to iD2 results in: ... – PowerPoint PPT presentation

Number of Views:33

Avg rating:3.0/5.0

Title: Subcircuits

1

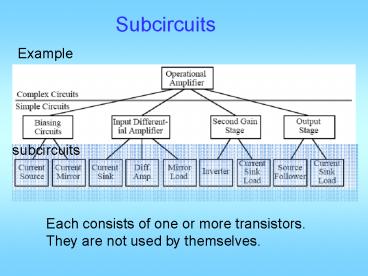

Subcircuits

Example

subcircuits

Each consists of one or more transistors. They

are not used by themselves.

2

Subcircuits

- Switches

- Diodes/active resistors

- Current mirrors

- Current sources/current sinks

- Current/voltage references

- Band gap references

3

MOS switches

Ideal Switch

MOS transistor as a switch

4

Non-idealities in a switch

5

Simple approximation

On operation VG gtgt VS or VD, VDS small, triode

A

B

Off operation VGS lt VT , cutoff

A

B

Very good off-char

6

(No Transcript)

7

Observations

- RON depends on W, L, VG, VT, VDS, etc

- RON is nonlinear (depending on signal)

Want RON small and constant

Strategies

- Use large W and small L to reduce RON

- Use large VGS to reduce the effect of signal

dependency - Use bootstrapping to increase VGS beyond VDDVSS

- Use constant VGS

- Use constant VB so as to have fixed VT

8

Effects of switch non-idealities

- Finite ON Resistance

- Non-zero charging and discharging time

- Limit settling

- Limits conversion rate

Actually takes time

Ideally instantaneous charging

9

- Signal level dependence of RON

- Different settling behavior at different signal

levels - Introduces nonlinearity

- Generate higher order harmonics

Vin pure sine wave

VC1 has harmonic distortions

10

- Finite OFF Current

- Leakage of a held voltage

- Coupling through the switch

- Accumulates with time

11

Clock Feed through

12

EXAMPLE - Switched Capacitor Integrator (slow

clock edge)

Assume

13

At t2

At t3

Once M2 turns on at t3, all charge on C1 is

transferred to C2

14

Between t3 and t4 additional charge is

transferred to C1 from the channel capacitance of

M2.

At t4

Ideal transfer

Total error

15

Charge injection

When switch is turned off suddenly, charges

trapped in the channel injected both either D and

S side equally.

The amount of trapped charges depends on the

slope of VG

16

U

slow regime

Hold value error on CHold

17

In the fast edge regime

Hold voltage error on CHold

Study the example in the book

18

Dummy transistor to cancel clock feed through

Complete cancellation is difficult. Requires a

complementary clock.

19

Use CMOS switches

Advantages - 1.) Larger dynamic range. 2.) Lower

ON resistance. Disadvantages - 1.) Requires

complementary clock. 2.) Requires more area.

20

Voltage doubler for gate overdrive

t2

t1

21

Constant VGS Bootstrapping

f0

f1

VG0

VDD

VGSVDD

22

When f1

Cp total parasitic capacitance connected to top

plate of C3.

23

PMOS version

off

on

24

Concept

Switched cap implementation

25

Summary on Switches

- To reduce RON

- Use large W and small L

- Use CMOS instead of NMOS or PMOS

- Use large VGS

- To reduce clock feed through

- Use cascode

- Use dummy transistor

- To reduce charge injection

- Use dummy

- Use slow clock edge

- Use complementary clock on switch and dummy

- To improve linearity

- Use large VGS

- Use vin-independent VGS

- Use vin-independent VBS (PMOS switch)

26

Diodes And Active Resistors

- Simple diode connection

- Voltage divider

- Extending the dynamic range

- Parallel MOSFET resistor

- Extending the dynamic range

- Differential resistor

- Single MOSFET

- Double MOSFET

27

Diode Connection

VDS VGS ? Always in saturation

If v gt VT, i gt 0 else i 0 ?diode

i

v

VT

28

Generally, gm 10 gmbs 100 gds

If VBS0,

29

Voltage Division

Equating iD1 to iD2 results in

VDS1 VDS2 VDD - VSS

Can use different W/L ratio to achieve desired

voltage division

30

Active vs passive resistors

Suppose Vo(VDDVSS)/2

2

gm1gm2bVEB100.22 m

Ro1/4m 250 ohm

Ro

Iob/2 (VEB)20.2mA

0

To achieve the same Ro, need two 500 ohm

resistors.

Io2/(2500)2mA, 10 times

Ro

Consumes 10 times more power

31

Extending Dynamic Range

Assume triode

32

(No Transcript)

33

Implementation

34

Parallel Transistor Realization

35

P-Channel Extended Range

36

Differential Resistor

37

(No Transcript)

38

Double MOSFET Differential Resistor

VSS

VSS

39

(No Transcript)

40

(No Transcript)

41

Current sources / sinks

V

Current source

I

I

Current sink

V

I

V

42

Non-ideal current sources / sinks

43

Two critical figures of merit

How flat the operating portion is How small the

non-operating region is

rout and vmin

For the simple sink on prev slide

44

Increasing Rout

45

Cascode Current Sink

46

(No Transcript)

47

Reduction of VMIN

rout rds1gm2rds2 is large which is good

But vmin vT 2VON needs to be reduced

48

Both just saturating

But the 2 IREFs must be the same. How?

49

M6 is ¼ the size, it requires 2 times over drive,

or 2 times VEB, or 2 time VON

Very flat

VMIN is much smaller

50

Alternative method

M5 is ¼ the size

Again, the 2 IREFs must be the same.

51

VON 0.6V

Larger W/L ratio can significantly reduce VON

52

Matching Improved by Adding M3

Why is it better now?

53

Regulated Cascode Current Sink

Near triode, VDS3?, iout ?, VGS4 ?, VD4 or VG5

?, Iout ?.

54

HW

- As we pointed out, the circuit on the previous

page suffers from a large Vmin. - Modify the circuit to reduce Vmin without

affecting rout. - Once you do that, VDS for M1 and M2 are no longer

match. Introduce another modification so that the

VDSs are matched.

55

56

(No Transcript)

57

Current Mirrors/Current Amplifiers

58

(No Transcript)

59

Simple Current Mirrors

Assuming square law model

60

If mCox and VT matched

If vDS matched

Current gain or mirror gain is controlled by

geometric ratio, which can be made quite accurate

61

Sources of Errors

- Mismatches in W/L ratios

- Use large W, L

- PLI

- Mismatches in mCox

- Large area, common centroid, higher order

gradient cancellation - Mismatches in vDS

- Make vDS the same

- Mismatches in VT

- Large area, cancel gradient, same VBS

62

l effect

63

VT mismatch effect

64

Sensitivity

A systematic way of computing errors.

r

65

Note common mode errors do not contribute to

matching errors, only differential errors do

Therefore, can take

66

Strategies to reduce errors

- Matching layout

- PLI, common centroid, symmetry, gradient,

- Increased area

- Matching operating conditions

- VD, VS, VB, current densities, ? use cascoding

to fix VDS - Reduce the sensitivies

- Use large VGS-VT

- Make equivalent l small, make go small, ? use

cascoding to reduce go

67

Straightforward layout to achieve mirror ratio of

4

Matching accuracy not good.

68

Will have better matching But only approximate

common centroid no pli can be more compact

HW suggest a better layout for ratio of 4.

69

Cascoding

M1 and M2 are the mirror pair that determines io.

VDS1 and VDS2 matched

go is small

70

Small signal model

71

(No Transcript)

72

Wilson Current Mirror

go is small

VDS1 and VDS2 not matched

73

Small signal circuit

74

Computation of rout

75

(No Transcript)

76

Improved Wilson Current Mirror

77

HW

In the improved Wilson current mirror What is

rout? What is Vmin? The resistance from D2 to

GND is 1/gm which is small. Why not connect G2 to

a constant bias to increase that impedance?

78

SPICE simulation

79

Regulated Cascode Current Mirror

Same as the regulated cascoded curren sink

VDS2 is very stable with respect to vo, but not

insensitive to Ireg change, not necessarily

better matching

80

Implementation of IREG using a simple current

mirror

81

Applications of current mirrors

Common source amplifier Load for C.S. Amp

82

Common drain amplifier (source follower)

83

Differential input single-ended output gain stage