Acknowledgement - PowerPoint PPT Presentation

1 / 1

Title:

Acknowledgement

Description:

Irish Research Council for Science, Engineering and Technology ... Web: http://birc.nuigalway.ie. 1. EMBRACE: Inspiration and Goals. 2. Spiking Neural Networks (SNN) ... – PowerPoint PPT presentation

Number of Views:1071

Avg rating:3.0/5.0

Title: Acknowledgement

1

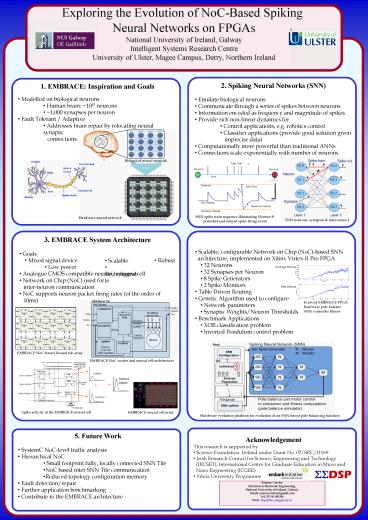

- 2. Spiking Neural Networks (SNN)

- Emulate biological neurons

- Communicate through a series of spikes between

neurons - Information encoded as frequency and magnitude

of spikes - Provide rich non-linear dynamics for

- Control applications, e.g. robotics control

- Classifier applications (provide good solution

given imprecise data) - Computationally more powerful than traditional

ANNs - Connections scale exponentially with number of

neurons

1. EMBRACE Inspiration and Goals

- Modelled on biological neurons

- Human brain 1013 neurons

- 1,000 synapses per neuron

- Fault Tolerant / Adaptive

- Addresses brain repair by relocating neural

synaptic connections

Biological neural network

SNN spike train sequence illustrating Neuron B

potential and output spike firing event

Hardware neural network

SNN neurons, synapses interconnect

- 3. EMBRACE System Architecture

- Goals

- Mixed signal device

- Low power

- Analogue CMOS compatible neuron/synapse cell

- Network on Chip (NoC) used for inter-neuron

communication - NoC supports neuron packet firing rates (of the

order of 10ms)

- Scalable, configurable Network on Chip

(NoC)-based SNN architecture, implemented on

Xilinx Virtex-II Pro FPGA - 32 Neurons

- 32 Synapses per Neuron

- 8 Spike Generators

- 2 Spike Monitors

- Table Driven Routing

- Genetic Algorithm used to configure

- Network parameters

- Synaptic Weights/Neuron Thresholds

- Benchmark Applications

- XOR classification problem

- Inverted Pendulum control problem

- Robust

- Scalable

- Reconfigurable

Average fitness

Best fitness

Evolved EMBRACE-FPGA hardware pole balance SNN

controller fitness

EMBRACE NoC-based Neural tile array

EMBRACE NoC-router and neural cell architecture

Spike activity in the EMBRACE neural cell

EMBRACE neural cell array

Hardware evolution platform for evolution of an

SNN-based pole balancing function

- .

- Acknowledgement

- This research is supported by

- Science Foundation Ireland under Grant No.

07/SRC/I1169 - Irish Research Council for Science, Engineering

and Technology (IRCSET), International Centre

for Graduate Education in Micro and Nano

Engineering (ICGEE) - Xilinx University Programme

- 5. Future Work

- SystemC NoC-level traffic analysis

- Hierarchical NoC

- Small footprint fully, locally connected SNN

Tile - NoC based inter SNN Tile communication

- Reduced topology configuration memory

- Fault detection/repair

- Further application benchmarking

- Contribute to the EMBRACE architecture

Seamus Cawley Electrical Electronic

Engineering, National University of Ireland,

Galway. Email seamuscawley_at_gmail.com Tel 353 91

493301 Web http//birc.nuigalway.ie