Design and Implementation of PowerAware Video Codec Systems - PowerPoint PPT Presentation

1 / 4

Title:

Design and Implementation of PowerAware Video Codec Systems

Description:

Power-Aware MPEG-4 Video Encoder System. Design Approach. Full Search ME Processor ... Efficient Reconfigurable DWT Processor for Flexible Video Codec Systems ... – PowerPoint PPT presentation

Number of Views:60

Avg rating:3.0/5.0

Title: Design and Implementation of PowerAware Video Codec Systems

1

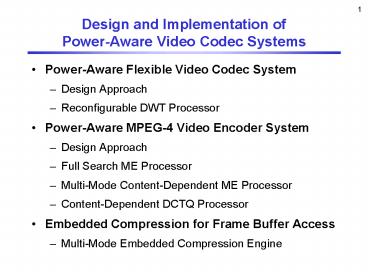

Design and Implementation ofPower-Aware Video

Codec Systems

- Power-Aware Flexible Video Codec System

- Design Approach

- Reconfigurable DWT Processor

- Power-Aware MPEG-4 Video Encoder System

- Design Approach

- Full Search ME Processor

- Multi-Mode Content-Dependent ME Processor

- Content-Dependent DCTQ Processor

- Embedded Compression for Frame Buffer Access

- Multi-Mode Embedded Compression Engine

2

Research Topics (1/3)

- Full Search ME Processor

- Practical low-power Full Search ME implementation

- Ultra low power dissipation

- 13.5 mW _at_ 1.35 V, 20 MHz, for CIF 30fps

- 1.5 mW _at_ 1.2 V, 2.5 MHz, for QCIF 15fps

- Much lower than existing Full Search ME

processors - Even lower than most Fast Search ME processors

- Multi-Mode Content-Dependent ME Processor

- Further reduce the power dissipation with

acceptable quality drop - Multi-mode ultra low power dissipation

- 51.3 mW 8.5 mW _at_ 1.8 V, for CIF 30fps

- Better power awareness

3

Research Topics (2/3)

- Reconfigurable DWT Processor

- Efficient Reconfigurable DWT Processor for

Flexible Video Codec Systems - 10 to 100 times power efficiency higher than DSPs

- Higher flexibility and HW efficiency than prior

arts - Reconfigurable and Scalable DWT PE Array

- Based on more computation-efficient Lifting

Scheme - A systematic design method leads to regular

lifting factorized structures - Support forward/inverse transforms

- Support variable filter kernel

- Reconfigurable WPT Address Generator

- Support variable decomposition level/structure

4

Research Topics (3/3)

- Content-Dependent DCTQ Processor

- Practical and efficient Content-Dependent DCT and

IDCT designs for power-aware video codec systems - Based on prior two designs, overcome their

drawbacks - Content-Dependent DCTQ Processor

- Content-Dependent DCT design

- Content-Dependent IDCT design

- Conventional Q and IQ designs

- 2.05 mW (worse case) and 1.06 mW (normal case)

for CIF 30 fps _at_ 1.8 V, 4.56 MHz - With only less than 0.1 dB quality drop