Task III: Novel Communications Mechanisms - PowerPoint PPT Presentation

1 / 34

Title:

Task III: Novel Communications Mechanisms

Description:

2. Evaluation of waveguide and free space performance for IFC Drivers. ... and hybrid prototypes to evaluate performance, process compatibility and cost. ... – PowerPoint PPT presentation

Number of Views:61

Avg rating:3.0/5.0

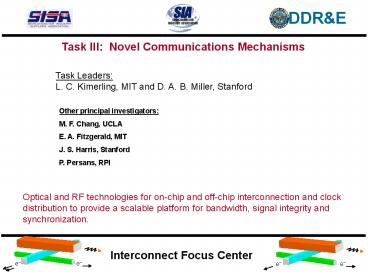

Title: Task III: Novel Communications Mechanisms

1

Task III Novel Communications Mechanisms

Task Leaders L. C. Kimerling, MIT and D. A. B.

Miller, Stanford

Other principal investigators M. F. Chang,

UCLA E. A. Fitzgerald, MIT J. S. Harris,

Stanford P. Persans, RPI

Optical and RF technologies for on-chip and

off-chip interconnection and clock distribution

to provide a scalable platform for bandwidth,

signal integrity and synchronization.

2

2010

Task III IFC Program Driver Targets

- 100 Tb/s on-chip

- 40 Tb/s off-chip

- 1010 grids

- Collaborative

?

- 5000 package pins

- Low latency

- Low power

- Low interference

- 3 GHz off-chip and global clock rates

- 10 GHz local clock rates

3

- Objectives

- 1. Technical analysis (w/Task 1,2) of RF/optical

interconnection with design criteria for

speed/power/area tradeoff. - 2. Evaluation of waveguide and free space

performance for IFC Drivers. - 3. Design-stabilized prototypes for early entry

applications such as testing and MCM/PWB

functions (w/Task 4). - 4. Monolithic and hybrid prototypes to evaluate

performance, process compatibility and cost. - 5. Novel architectures free space and optical

buss prototypes (w/Tasks 1,2). - Demonstration of GHz clock and data distribution

functions. - Scalability of broadcast interconnects.

- Approaches

- 1. Analyze approaches and define likelihood of

success using speed/power/crosstalk metrics. - 2. Evaluate optical chip I/O and clock

distribution functions. - 3. Develop CAD tools for device design,

component integration and partitioning of

optics/electronics (w/Tasks 2,6). - 4. Develop materials and processes for

integration on silicon (w/Task 5). - 5. Prototype hybrid and monolithic architectural

platforms for IFC Drivers, and assess the limits

of scalability of performance and integration. - Develop entry-level functionality for e-test and

MCMs (w Task 4).

4

MONOLITHIC SILICON MICROPHOTONICS

L.C. Kimerling, MIT Materials Processing Center

APPROACH To create technology building blocks

under the constraints of conventional fabline, IC

design and systems performance requirements.

- MILESTONES

- Low loss Si nanowaveguides

- Integrated SiEr LED / CMOS driver

- Si microresonator devices

- 16x fanout clock signal

- Vertically coupled architectures

- Ge on Si photodetectors

- Wafer bonded isolation/integration

ND1x107cm-2

Responsivity (A/W)

ND2x107cm-2

1x8 MMI

ND109cm-2

7.5 mm

Bias Voltage (V)

5

OPTICAL BUS ARCHITECTURE

- chip testing

- clock distribution

- on-chip I/O

- MCM/PWB architectures

- ethernet I/O

Optical Signal Distribution

off-chip source

waveguides (polySi)

splitters and bends

photodetectors (Ge)

6

COMPONENTS FOR OPTICAL INTERCONNECTION

- Si/SiO2 Waveguides

- index contrast Dn2

- small dimensions

- low cross-talk

- small radius bend

- multi-level interconnection

- Ge Photodetectors

- Si process compatibility

- l 1.3-1.55mm performance

- indirect bandgap

- 4 lattice mismatch

7

H.T.C. Waveguide Bends and Splits

- High Transmission Cavity (HTC) waveguide bends

- area 0.5 mm2

- loss 0.320.05 dB/turn

- vs. 0.420.05 dB/turn for 1 mm bend on the same

die.

- High Transmission Cavity (HTC) waveguide

junctions - loss of 1 dB

- non-uniformity s/m 0.2 (will be improved by

design) - Designed with C. Monolato and H. Haus, MIT

- Fabricated with P. Maki at MIT Lincoln Labs

8

Silicon Racetrack Response

Fabricated by 248nm Lithography! Q 2000, FSR16

nm

Silicon

Silica

6 um

Drop

In

Fabricated with P. Maki at MIT Lincoln Labs

9

High order filters (Silicon Nitride)

10

1x4 WDM in Silicon Nitride

Efficiency 100, Q500 Co-Workers B. E. Little

, H. A. Haus, MIT Devices fabricated at MIT

Lincoln Labs with Paul Maki

Thru-port

Thru-port

1

2

3

4

11

Threading dislocation free, direct Ge on Si

Photodetectors

Ge

SiO2

SiO2

SiO2

Si

12

Process Design

550C

300C

Deposit flat Ge epilayer on Si by a two-step CVD

process.

13

Defect Reduction

Cyclic Thermal Annealing

As Grown Ge on Si

After Dislocation Annihilation Anneal

14

Performance

-V

nGe

V

Ge

pSi

330 mA/W with 1 mm Ge 550 mA/W with 4 mm Ge 770

mA/W with AR Coating

15

PIN Ge Photodetectors Speed

FWHM 1ns

16

MONOLITHIC III-V on SILICON E.A. Fitzgerald, MIT

Materials Processing Center

- OBJECTIVE

- To establish an IC compatible, monolithic process

technology for integration of III-V

optoelectronic devices with Si CMOS

MILESTONES III-V LEDs and lasers on Si

Creation of a relaxed SiGe/Si co-planar substrate

technology III-V LEDs and lasers on such

co-planar substrates Demonstration of optical

link on Si

APPROACH To create III-V LEDs and lasers on Si

substrates using intermediate SiGe interlayers.

GaAs and InGaAs emitters on Ge/SiGe/Si

substrates Development of co-planar SiGe/Si

technology useful for both III-V integration and

SiGe detector integration

co-planar SiGe/Si

GaAs on Si

Ge

17

Monolithic Si/SiGe/GaAs

GaAs

SiGe

Ge

TDD 18

InGaAs Graded Buffer on Ge/SiGe/Si

XV TEM

PV TEM

GaAs

InGaAs

Ge

TEM picture showing the relaxation which leads to

the larger lattice constant near GaAs on

Ge/SiGe/Si

19

Preliminary designs - Laser 2

New top-contact laser designs

3,4,5,7,10,15,20, 40 um oxide cuts

50 um

100um

50 um

50 um

n SiGe/Ge

100um

n SiGe/Ge

100um

Si substrate

Si substrate

4 Masks w/o mesa

5 Masks w/ mesa

20

New Design for Optical Links

- Confinement of light in waveguide through

- high metal reflectivity

- index difference between Al0.5Ga0,5As and

- Al0.9Ga0.1As

- Ge absorbs stray light

- DBRs added to increase the reflectivity at

- the bottom waveguide interface

- 4 pairs of Al0.95Ga0.05As/Al0.05Ga0.95As

- alternating layers

21

- III-V DEVICE TECHNOLOGY

- James Harris, Stanford

- Low Temperature GaAs for Optical Interconnect

Receivers - Si-CMOS compatible

- High sensitivity

- Ultra-fast response (

- Low voltage operation

22

Solder-Bonding Technique

Processing of GaAs wafer Etch through n region,

and implant p Evaporate p contact Evaporate n

contact Electroplate 5-10mm of indium on top of

contacts Mesa etch through AlGaAs stop

layer Processing of Silicon chips Cast the Si

chip in black wax Evaporate 1.5 mm of metal onto

chip for contacts Bonding of two wafers Bond Si

and GaAs chips Flow epoxy between two

chips Remove GaAs substrate by using a selective

GaAs/AlGaAs etch AR coat devices

23

- GaInNAs for Long Wavelength, Low Voltage Optical

Interconnects - Scaled CMOS compatible (

- Si substrate transparent

- Applicable to modulators, VCSELs and detectors

- Compatible with telecommunications wavelengths

24

Opportunity Optical Clock Distribution Tasks

1,2,3

- Approach

- off-chip optical source

- distribute by waveguides

- optoelectronic conversion detector and

reciever circuit - local electrical clock distribution

- Potential Advantages

- low skew distribution of optical signals,

thus very high speed clocking - low noise

- power reduction

25

(No Transcript)

26

OPTICAL INTERCONNECT PERFORMANCE

D. A. B. Miller, Ginzton Lab, Stanford

OBJECTIVE To establish which interconnect

functions are best performed optically how best

to perform them

- MILESTONES

- Define target performance metrics for

optoelectronic devices and optics. - Identify implementation path for key functions.

APPROACH Analyze, clock distribution, on-chip

interconnects and off-chip interconnects for

device options (lasers, modulators,

photodetectors) optics options (free-space,

fibers, waveguides) CMOS driver and receiver

circuit issues (power, crosstalk, latency)

100000

100000

t

Compute BW

u

t

Comp BW

10000

u

10000

t

w

Electrical I/O BW

Elec I/O BW

u

t

u

I/O BW

Optical I/O BW

u

1000

t

w

1000

w

u

w

t

Compute Bandwidth (Gbit/s) Gates x

Clock-Speed

I/O Bandwidth (Gbit/s) I/Os x Clock-Speed

100

SIA Predictions

w

u

t

100

w

t

u

10

w

w

10

1

1

0.1

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

Line width (microns)

27

Hybrid Prototype and Electronics Performance

- Construction of test systems for interconnections

to silicon chips - Design and fabrication of new silicon chips

- 2nd gen. dense array chip for parallel and WDM

interconnects - circuits to test latency of optical interconnects

on silicon chips - concepts for receiverless optical interconnects

- circuits for short pulse interconnects

- parallel VCSEL interconnects with clock and

shared reference channel - Current status

- chips designed, fabricated, and electrically

tested - optical testing started on VCSEL interconnect

- receiverless optical interconnects ready to start

testing - 2nd gen. WDM ready to start testing

- optoelectronics being bonded for testing other

chips

28

Chip to test latency of optical links

- 2 x 2 mm chip in 0.25 µm CMOS, with modulator

outputs - receiver circuits, clocked and asynchronous, with

electrical samplers to measure internal

performance - ring oscillators with internal optical links for

latency tests - transmitter-receiver circuits for pump-probe

ultrafast latency tests - low capacitance silicon photodetectors to test

principle of receiverless links with ultra-low

latency

circuit layout for low capacitance (22 fF)

silicon photodetector pair to generate logic

levels without amplification (receiverless)

29

Chip for linear array testing with VCSELs and

modulators

- test concept of shared clock/reference level

channel for linear array of optical interconnects

in 2 x 2 mm 0.5 µm CMOS chip - test comparison of VCSEL (vertical cavity surface

emitting laser) and modulator links - operate full links with delay-locked loop for

clock recovery and on-chip bit error rate testing

CMOS chips

VCSEL/MSM chip

30

2nd Generation WDM Interconnect Chip and Optics

- 2 x 2 mm 0.5 µm CMOS chip

- design for improved array performance

- 2nd generation receiver

- 2nd generation WDM optics

PRBS generator

Controlled noise generator

transceiver arrays

BER tester

31

- CMOS Compatible Waveguides and Couplers

P D Persans, Rensselaer Polytechnic Institute

Goals Develop and evaluate materials and

processes for fabrication of optical waveguides

and couplers for on-chip, MCM, and 3D chip

architectures. Motivation Optical waveguides

provide high bandwidth, low dispersion, low

cross-talk alternatives to wire for chip to chip

and through chip 3D interconnects telecommunicatio

ns switching.

Constraints Materials and processing must Be

compatible with CMOS back-end and/or new 3D

processes and designs Be compatible with either

monolithic or bump-bonded optoelectronics Have

cross sections from sub-micron (on-chip) to 10

micron (coupling off chip) Provide vertical

(V), horizontal (H), and V to H guides and

couplers.

32

3D and MCM Applications

- Polymer waveguide processing and characterization

- evaluation of photosensitive fluorinated

polyimides in slabs and as waveguides - effects of processing on interface roughness and

loss in polyimides - preliminary evaluation of Si-based epoxy polymers

(low loss ( - thermal and chemical stability

- Inorganic and polymer/inorganic structures

- plasma-deposited SiO2, Si3N4 multilayers for

mirrors, bending elements, couplers - investigation and modeling of wet-etch undercut

for mirrors - adhesion and use of sacrificial layers for

undercut - AFM surface roughness analysis

BOE undercut SiO2

3x8 micron polyimide waveguide

33

RF Interconnects M. Frank Chang, University of

California, Los Angeles

- Concept

- Conventional approaches based on passive metal

interconnects may eventually encounter

fundamental limits and impede the future ULSI

advancement - Propose to develop an active and

reconfigurable RF-Interconnect based on

high-speed (up to 150 Gbps/channel) and

dispersion-free signal transmission and

multiple-access communication algorithms

Wireless LAN inside a MCM

Shared Co-Planar Wave Guide

- Goals

- Quantify advantages of the RF-Interconnect system

- Identify and develop enabling technologies (based

on mainstream CMOS and MCM) to high performance,

low-cost RF-interconnects

- Tasks

- RF-Interconnect system design and analysis

- I/O channeling and multiple access

- T/R circuit integration

- Fault-tolerant ULSI system architecture based on

RF-Interconnect

34

Task III IFC Research Drivers

- Single Chip Network Element

- 40 Tb/s off-chip optical I/O

- 100 Tb/s optical on-chip bisection bandwidth

- Global optical/RF synchronization

- Reconfiguration

- Collaborative Node

- All of the above

- Inter-node RF/optical communication

- 3D integration