The Arithmetic Operations - PowerPoint PPT Presentation

1 / 21

Title:

The Arithmetic Operations

Description:

N.B: In each of the above cases : Zero, Sign, Carry/Borrow ... (Fed Thro MUX) A / NOT A. Operand # 2 (Fed Thro MUX) B / NOT B / 0...0 / 1...1. n. OVERFLOW ... – PowerPoint PPT presentation

Number of Views:126

Avg rating:3.0/5.0

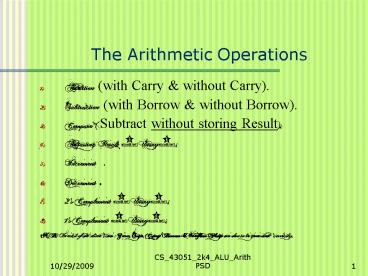

Title: The Arithmetic Operations

1

The Arithmetic Operations

- Addition (with Carry without Carry).

- Subtraction (with Borrow without Borrow).

- Compare ( Subtract without storing Result).

- Adjusting Result Unary.

- Increment .

- Decrement .

- 2s Complement Unary.

- 1s Complement Unary.

- N.B In each of the above cases Zero, Sign,

Carry/Borrow Overflow Flags are also to be

generated correctly.

2

The Arithmetic Operations Operands

- BINARY OPERATIONS (for both SIGNED

UNSIGNED) - Sl. No. Operation O/P Logical Expression

ALU Function Code - 1. ADD with Cy A PLUS

B PLUS Cy_Flag 0 0 0 0

0 - 2. SUBTRACT A PLUS (NOT B)

PLUS (NOT Cy_Flag) 0 0 0 0 1 - with BORROW

- 3. COMPARE A PLUS (NOT B)

PLUS (C_In 1) 0 0 0 1 0 - All Flags are set.

Result generated is IGNORED - 4. INCREMENT A PLUS (B 00)

PLUS (C_In 1) 0 0 0 1 1 -

Inhibit affecting Cy OV Flags - 5. DECREMENT A PLUS (B1.1) PLUS

(C_In 0) 0 0 1 0 0 -

Inhibit affecting Cy OV Flags - UNARY OPERATIONS (Applicable for

BIT Operands) ALU Function Code - 6. COMPL A ( NOT A) PLUS

(B0..0) PLUS (C_In1) 0 0 1 0 1 - 7. PASS A A PLUS

(B0. 0) PLUS (C_In0) 0 0 1 1 0

- 8. NOT A ( NOT A)

PLUS (B0 0) PLUS (C_In0) 0 0 1 1 1 - _

3

The Adder cum SUBTRACTER Unit

Operand 1 (Fed Thro MUX) A / NOT A

Operand 2 (Fed Thro MUX) B / NOT B / 00 / 11

n

n

Cy_Flag / 0 / 1/ NOT (Cy_Flag) Thro MUX

CARRY/BORROW

n Bit ADDER

n bit Arithmetic Result C

OVERFLOW

N.B Op Codes are used as various MUX Controls

4

The Selection Logic of Operand 1

n bits

A

NOT A

8 1, n bit Group Mux

S 2

S 1

S 0

To Adder I/P Operand 1

n bits

5

The Selection Logic of Operand 2

From n bit wide Inputs

0

1

B

NOT B

8 1, n bit Group Mux

S 2

S 1

S 0

To Adder I/P Operand 2

n bits

6

The Selection Logic of CY

From 1 bit wide Inputs

0

1

Cy

NOT Cy

8 1, 1 bit Mux

S 2

S 1

S 0

To Adder Cin Input

1 bit

7

Inside the n bit Adder

Op1(i-1)

Op1i

Op10

Op2i

Op2(n-1)

Op2(i1)

Op2(i-1)

Op20

Op1(n-1)

Op1(i1)

1 bit ADDER

1 bit ADDER

1 bit ADDER

1 bit ADDER

1 bit ADDER

Cy(i)

Cy(i-1)

Cy0

c0

Cy(i1)

c(n-1)

c(i1)

ci

c(i-1)

Cy(i-2)

OvFl

Cy_in C_In

Cy(n-2)

Cyout

8

A typical Adder Cell Structure

Inputs to the ith Stage

Op1 i

Op2 i

The ith Adder Cell

Cy(i-1) generated by The Previous (i-1) th

Stage

Cy(i) fed To the NEXT (i1) th Stage

ith Bit of the Result ci Sumi

9

Adder Table

- Op1i Op2i CY(i-1) CY(i) Sumi

- --------------------------------------------------

----------- - 0 0 0 0

0 - -----------------------------------------

- 0 0 1 0 1

- ------ -------------------------------------------

------------ - 0 1 0 0

1 - -------------------------------------------

- 0 1 1 1 0

- --------------------------------------------------

------------ - 1 0 0 0 1

- -----------------------------------------

- 1 0 1 1 0

- --------------------------------------------------

----------- - 1 1 0 1

0 - -------------------------------------------

- 1 1 1 1 1

10

Limitations of this Cell

- 1) Outputs generated Result Sumi as well as

Cy(i) depend not only on the Current Inputs but

are also dependent on the Previous Stage output

Cy(i-1) which represents one of the inputs. - 2) The carry / borrow input to any stage

depends on ALL its previous stages output thereby

forcing a Rippling Effect, in which case each

ADDER stage contributes to the output generation

time of all the next stages. - 3) Worst Case Delay (due to rippling of Carry)

happens to be n stage delay for any n bit

Adder/SUBTRACTER. - Objective To reduce this delay by exploring

alternative schemes of Carry Generation.

11

The Output Logical Expressions

- The Sum / Result Output

- Sumi Op1i ? Op2i ? Cy(i-1) ----- a

- The Carry Output

- Cy i Op1i .Op2i Cy(i-1).(Op1i Op2i )- b

- gi Cy(i-1). pi ---- c

- Where gi Local Carry Generate Op1i .Op2i -

d - pi Prev. Carry Propagate Op1i Op2i - e

- It can be shown that Sumi gi ? pi ? Cy(i-1)

----- f - Proof left as an exercise

- N.B Both gi pi depends on the Current stage

Inputs only.

12

The Output Logical Expressions for 1st bit

(LSBs) of a 4 bit Adder

- The Sum / Result Output

- Sum0 Op10 ? Op20 ? Cin ----- a0

- The Carry Output

- Cy 0 Op10 .Op20 Cin.(Op10 Op20 )- b0

- g0 Cin. p0 ---- c0

- Where g0 Local Carry Generate Op10 .Op20 -

d0 - p0 Prev. Carry Propagate Op10 Op20- e0

- Sum0 g0 ? p0 ? Cin ----- f0

13

The Output Logical Expressions for 2nd bits

of a 4 bit Adder

- The Sum / Result Output

- Sum1 Op11 ? Op21 ? CY0 ----- a1

- The Carry Output

- Cy 1 Op11 .Op21 CY0.(Op11 Op21 )- b1

- g1 CY0. P1 - c1

- g1 (g0 Cin. p0). p1 (From c0) c11

- Where g1 Local Carry Generate Op11 .Op21 -

d1 - p1 Prev. Carry Propagate Op11 Op21- e1

- Sum1 g1 ? p1 ? CY0 , after substitution

- Sum1 g1 ? p1 ? (g0 Cin. p0) ----- f1

14

The Output Logical Expressions for 3rd bits

of a 4 bit Adder

- The Sum / Result Output

- Sum2 Op12 ? Op22 ? CY1 ----- a2

- The Carry Output

- Cy 2 Op12 .Op22 CY1.(Op12 Op22 )- b2

- g2 CY1. P2 g2 (g1 CY0. p1). p2

( From c1) - g2 (g1 (g0 Cin. p0). p1). p2 c2

- Where g2 Local Carry Generate Op12 .Op22 -

d2 - p2 Prev. Carry Propagate Op12 Op22- e2

- Sum2 g2 ? p2 ? CY1, after substitution

- Sum2 g2 ? p2 ? (g1 (g0 Cin. p0). p1) -----

f2

15

The Output Logical Expressions for 4th bits

MSBs of a 4 bit Adder

- The Sum / Result Output

- Sum3 Op13 ? Op23 ? CY2 ----- a3

- The Carry Output

- Cy 3 Op13 .Op23 CY2.(Op13 Op23 )- b3

- g3 CY2. p3

- After substituting from c2

- g3 (g2 (g1 (g0 Cin. p0). p1). p2).

p3 c3 - Where g3 Local Carry Generate Op13 .Op23 -

d3 - p3 Prev. Carry Propagate Op13 Op23- e3

- Sum3 g3 ? p3 ? CY2 after substitution

- Sum3 g3 ? p3 ? (g2 (g1 (g0 Cin. p0). p1).

p2)- f3

16

The Simultaneous Carry Cy Generation Scheme

Op1(n-1)

Op1(i1)

Op1(i)

Op1(i-1)

Op1(0)

Op2(n-1)

Op2(i-1)

Op2(0)

Op2(i1)

Op2(i)

P-G Gen

P-G Gen

P-G Gen

P-G Gen

P-G Gen

g(i-1)

p(n-1)

p(i1)

p(i-1)

g(n-1)

g(i1)

g(0)

p(0)

p(i)

g(i)

Carry Generator Block

Cin

Cy(i1)

Cy(i)

Cy(i-1)

Cy (0)

Cy OUT

17

The Sum Generation Scheme

Op1(n-1)

Op1(i1)

Op1(i)

Op1(i-1)

Op1(0)

Op2(n-1)

Op2(i-1)

Op2(0)

Op2(i1)

Op2(i)

P-G Gen

P-G Gen

P-G Gen

P-G Gen

P-G Gen

g(i-1)

p(n-1)

p(i1)

p(i-1)

g(n-1)

g(i1)

g(0)

p(0)

p(i)

g(i)

Sum Generator Block

Cin

Sum(i1)

Sum(i)

Sum(i-1)

Sum (0)

Sum(n)

18

The Overflow Generation - 1

- Op1(n-1) Op2(n-1) C(n-1)

OpR OVFLow - --------------------------------------------------

----------------------- -

( 0 ? ADD , 1 ? SUB) - --------------------

--------------------------------------- - 0

0 0 0 0 -

------ -------------------------------------------

----------------------------------- -

0 0 1

0 1 - --------------------

-------------------------------------- - 0

1 X 0 0 -

--------------------------------------------------

--------------------------------- - 1

0 X 0 0

- -------------------

-------------------------------------- - 1

1 1 0 0 -

--------------------------------------------------

------------------------------- -

1 1 0

0 1 - -------------------

------------------------------------

19

The Overflow Generation - 2

- Op1(n-1) Op2(n-1) C(n-1)

OpR OVFLow - --------------------------------------------------

----------------------- -

( 0 ? ADD , 1 ? SUB) - --------------------

--------------------------------------- - 0

0 X 1 0 -

------ -------------------------------------------

----------------------------------- -

0 1 0

1 0 - --------------------

-------------------------------------- - 0

1 1 1 1 -

--------------------------------------------------

--------------------------------- - 1

1 X 1 0

- -------------------

-------------------------------------- - 1

0 1 1 0 -

--------------------------------------------------

------------------------------- -

1 0 0

1 1 - -------------------

------------------------------------

20

The Overflow Generation - 3

- Overflow Cyout(n-1) ? cyi(n-2) ----- 1

- i.e. Overflow Cy out of Sign ? Cy into Sign

- Provided Carry into Sign bit I.e. carry into

msbit becomes accessible. - Proof Left as an Exercise

21

The Flag Generation Schemes

- Sign Flag Msbit of Result.

- Zero Flag c(n-1) OR c(n-2) OR ..

- ci OR c(i1) OR .. C0

- Carry/Borrow Flag As generated.

- Overflow Flag As generated