R - PowerPoint PPT Presentation

Title: R

1

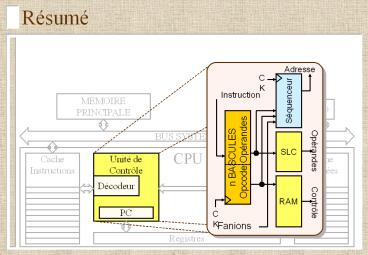

Résumé

2

Résumé

Adresse

PC

1

CK

Offset

SLC

Opcode

Condition

Fanions

3

Résumé

PC ? adresse initiale

MAR ? PC MDR ? MMAR IR ? MDR

CK

décodification de IR

contrôle?

NON

OUI

saut?

adresse?

OUI

NON

OUI

NON

chargement

exécution

PC?PC offset

PC?PC1

4

Complication 1

- Comment peut fonctionner un processeur 8 ou 16

bits quand les instructions doivent coder

tellement d'informations? ou - Comment réaliser des instructions qui nécessitent

plus d'opérandes que ne peut coder un seul mot

mémoire? ou - Comment exécuter des instructions qui nécessitent

plusieurs coups d'horloge? - Une solution possible la microprogrammation.

5

Décodage - Processeurs câblés

6

Décodage - Microprogrammation

Mémoire

MDR

MAR

OPCODE ...000 Microinstruction 1

Microinstruction 2 ...

Microinstruction N ...001 Microinstruction 1

Microinstruction 2 ...

Microinstruction N ...011 Microinstruction

1 ...010 Microinstruction 1 ......

.........................

CK

PC

Séquenceur

Microprogrammes

IR Opcode Opérandes

Opérandes

Contrôle

CK

Fanions

7

Décodage - Microprogrammation

Mémoire

MDR

MAR

OPCODE ...000

...001 ...011

......................... ...010

......................... ......

.........................

CK

PC

Séquenceur

S0

S1

S2

Sn

Microprogrammes

S0

S1

S2

Sn

S3

IR Opcode Opérandes

Opérandes

Contrôle

CK

Fanions

8

Exemple - Motorola 68000

- Architecture 16 bits (extensions 32 bits)

- 12 modes d'adressage

- 16 fanions

- 8 registres de 16 (32) bits de large

- Exemple 1 addition (en BCD) des contenus de deux

adresses stockées dans deux registres, avec

pré-décrément des adresses - abcd -(A1),-(A2)

- Exemple 2 soustraction d'un nombre immédiat (16

bits) au contenu d'une position mémoire (adresse

16 bits) - subi.0 0f0fH,2d52H

Mémoire

MDR

MAR

CK

PC

Séquenceur

Microprogrammes

IR Opcode Opérandes

Opérandes

Contrôle

CK

Fanions

9

Exemple 1 - Codage de l'instruction

abcd -(A1),-(A2)

Mémoire

1 mot de 16 bits est suffisant pour coder cette

instruction

MDR

MAR

CK

PC

Séquenceur

1 1100 010100 001001

Destination Source

Microprogrammes

IR Opcode Opérandes

Opérandes

Il faut remarquer que le contenu de la

destination est écrasé par le résultat. On peut

supposer que le processeur contient une seule

ALU.

Contrôle

CK

Fanions

10

Exemple 1 - Décodage de l'instruction

Mémoire

abcd -(A1),-(A2)

MDR

MAR

CK

PC

Séquenceur

A1?A1-1

Microprogrammes

A2?A2-1

IR 1100010100001001

Opérandes

MA1?MA2MA1 PC?PC1 IR?MPC

Contrôle

CK

Fanions

11

Exemple 2 - Codage de l'instruction

subi.0 0f0fH,2d52H

Mémoire

3 mots de 16 bits sont nécessaires pour

coder cette instruction

MDR

MAR

CK

PC

Séquenceur

1 0000 010001 111000

Taille des données Mode d'adressage

Microprogrammes

IR Opcode Opérandes

Opérandes

2 0000111100001111

Immédiat

Contrôle

3 0010110101010010

CK

Fanions

Adresse

12

Exemple 2 - Décodage de l'instruction

Mémoire

subi.0 0f0fH,2d52H

MDR

MAR

CK

PC

Séquenceur

PC?PC1 IR?MPC

A1?IR PC?PC1 IR?MPC

Microprogrammes

IR 0000010001111000

Opérandes

MIR?MIR-A1 PC?PC1 IR?MPC

Contrôle

CK

Fanions

13

Complication 2

- Existe-t-il des architectures alternatives pour

l'unité de traitement permettant de réduire la

complexité des instructions? - La réponse est (évidemment) oui.

- Malheureusement, une telle réduction implique

une perte de performance si les instructions

sont plus simples, il faut plus d'instructions

pour une tâche donnée. - On échange une complexité matérielle contre une

complexité logicielle.

14

Architecture "standard" - Structure

INPORT

OUTPORT

OEN

1 0

SEL

I0

I1

AL2 AL1 AL0

Z

Z?0

SH2 SH1 SH0

SHIFTER

3

RA

R0

R1

R2

R3

R4

R5

R6

R7

3

RB

WEN

3

WA

15

Architectures "standards" - Exemple

- Langage de haut niveau

- P (QR ST)(U V)

- Compilation pour une architecture "standard"

- MULT Q,R R ? QR

- MULT S,T T ? ST

- ADD T,R R ? QR ST

- ADD U,V V ? U V

- MULT R,V V ? (QR ST)(U V) MOVE V,P

P ? (QR ST)(U V)

16

I - Architectures load/store

- Une première possibilité a déjà été mentionnée.

Il s'agit de limiter toute référence à la mémoire

principale aux seules instructions de transfert

de données (move, load, store). Par exemple,

l'instruction - abcd -(As),-(Ad)

- peut être transformée en

- dec As

- dec Ad

- move (As),Ax

- move (Ad),Ay

- abcd Ax,Ay

- move Ay,(Ad)

- Ce type d'architecture est appelé load/store

(chargement-rangement).

17

Architectures load/store - Structure

INPORT

OUTPORT

OEN

I0

I1

AL2 AL1 AL0

Z

Z?0

SH2 SH1 SH0

SHIFTER

1 0

SEL

3

RA

3

RB

WEN

3

WA

18

Architectures load/store - Exemple

- Langage de haut niveau

- P (QR ST)(U V)

- Compilation pour une architecture load/store

- LOAD R1, Q

- LOAD R2, R

- MULT R1,R2 R2 ? QR

- LOAD R1, S

- LOAD R3, T

- MULT R1,R3 R3 ? ST

- ADD R2,R3 R3 ? QR ST

- LOAD R1, U

- LOAD R2, V

- ADD R1,R2 R2 ? UV

- MULT R2,R3 R3 ? (QR ST)(UV)

- STORE R3,P P ? (QR ST)(UV)

19

II - Processeurs à accumulateur

- Dans ce type d'architecture les résultats de

toutes les opérations sont stockés dans un

registre particulier (l'accumulateur) et toutes

les variable sont stockées dans la mémoire

principale. - Par exemple, l'opération x ? y z est réalisée

par - load y ACC ? y

- add z ACC ? ACC z

- store x x ? ACC

- Chaque instruction doit donc contenir deux

champs l'opcode et l'adresse de l'opérande

(l'accumulateur est toujours un opérande par

défaut). - Exemples DEC PDP-8, Intel 8080, Motorola 6800.

20

Processeurs à accumulateur - Structure

INPORT

OUTPORT

OEN

I0

I1

AL2 AL1 AL0

Z

Z?0

SH2 SH1 SH0

SHIFTER

0 1

SEL

Accumulateur

21

Processeurs à accumulateur - Exemple

- Langage de haut niveau

- P (QR ST)(U V)

- Compilation pour une architecture à accumulateur

- LOAD Q ACC ? Q

- MULT R ACC ? QR

- STORE P P ? QR

- LOAD S ACC ? S

- MULT T ACC ? ST

- ADD P ACC ? QR ST

- STORE P P ? QR ST

- LOAD U ACC ? U

- ADD V ACC ? UV

- MULT P ACC ? (QR ST)(UV)

- STORE P P ? (QR ST)(UV)

22

III - Processeurs à pile (stack)

- Dans ce type d'architecture les opérandes se

trouvent toujours au sommet d'une pile (stack),

typiquement dans la mémoire, et le résultat est

ensuite toujours stocké au sommet de la pile. En

conséquence, une instruction typique ne contient

pas d'adresse d'opérande. Un registre dédié, le

stack pointer (SP), pointe toujours le sommet de

la pile. - Par exemple, l'opération x ? y z est réalisée

par - push y SP ? SP1 MSP ? y

- push z SP ? SP1 MSP ? z

- add SP ? SP-1

- MSP ? MSP MSP

- pop x SP ? SP-1 x ? MSP

- Exemples Burroughs B5000, HP 300.

23

Processeurs à pile - Structure

INPORT

OUTPORT

Adresse

MSP

MSP

POP

PUSH

1

0

-1

I0

I1

AL2 AL1 AL0

0 1

Z

Z?0

SH2 SH1 SH0

SHIFTER

SP

Stack Pointer

0 1

SEL

SP

24

Processeurs à pile - Exemple

- Langage de haut niveau

- P (QR ST)(U V)

- Compilation pour une architecture à pile

- PUSH Q SP ? SP1 MSP ? Q

- PUSH R SP ? SP1 MSP ? R

- MULT SP ? SP-1 MSP ? QR

- PUSH S SP ? SP1 MSP ? S

- PUSH T SP ? SP1 MSP ? T

- MULT SP ? SP-1 MSP ? ST

- ADD SP ? SP-1 MSP ? QR ST

- PUSH U SP ? SP1 MSP ? U

- PUSH V SP ? SP1 MSP ? V

- ADD SP ? SP-1 MSP ? UV

- MULT SP ? SP-1 MSP ? (QR ST)(UV)

- POP P SP ? SP-1 P ? (QR ST)(UV)