Chip - PowerPoint PPT Presentation

Title: Chip

1

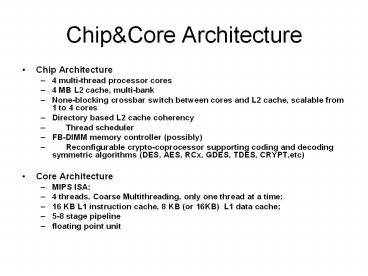

ChipCore Architecture

- Chip Architecture

- 4 multi-thread processor cores

- 4 MB L2 cache, multi-bank

- None-blocking crossbar switch between cores and

L2 cache, scalable from 1 to 4 cores - Directory based L2 cache coherency

- Thread scheduler

- FB-DIMM memory controller (possibly)

- Reconfigurable crypto-coprocessor

supporting coding and decoding symmetric

algorithms (DES, AES, RCx, GDES, TDES, CRYPT,etc) - Core Architecture

- MIPS ISA

- 4 threads, Coarse Multithreading, only one thread

at a time - 16 KB L1 instruction cache, 8 KB (or 16KB) L1

data cache - 5-8 stage pipeline

- floating point unit

2

Why Multi-thread core

- To reduce the effect of memory access bottleneck

When a thread must wait for memory, just switch

to another thread, hide the memory latency

problem. - With a lessened effective penalty for memory

misses we can make branch prediction less

aggressive, which means easier development and a

smaller, simpler core. - We also planned to have a hardware thread

scheduler, which can balance overall workload by

dispatching threads to appropriate cores. This

part will be coupled with commercial OS, as

LINUX. - Each MIPS processor will be able to be connected

in an efficient manner to the Reconfigurable

crypto-coprocessor. This will be done through

specific network.

3

(No Transcript)

4

Multicore architecture

- TLP et RPU

- Reconfigurable Interconnections

- Complexity management

- Embedded reliability

- Energy management

- Advanced technologies

- Reconfigurable coprocessors

OS

Scheduling,

Switch and interconnection

RISC core

RISC core

L2

L2

L1

L1

RISC core

RISC core

L1

L1

RISC core

RISC core

L1

L1

RPU fg core

RPU cg core

L1

L1

5

1er issue Parallelism management

- L1 cache design

- High performance cache

- Full custom cache design

- Memory management

- Memory hierarchy

- Multibank memory

- System design

- Considering, at the same time, both sw and hw

aspects - Embedded thread controller

- QoS functionnalities

- Shared ressources

M2

6

2nd issue Interconnections

- High performance Interconnections networks

- Reconfigurable Dynamic configuration

- Asynchronous

- Advanced design

- I/O management

- HW and embedded SW design

Thread Controller

M2

Multi-bank L2 cache

7

3rd issue Reconfigurable cryptoprocessor

- High performance cryptoprocessor

- For high data rate

- Symetric cryptography

- Multi-mode cryptography

- On the fly reconfiguration

- Highly interconnected to processor, memory and I/O

Thread Controller

I/O

R. Crypto Coprocessor.

M2

Multi-bank L2 cache

8

- 3 RD areas

- Parallelism management

- Interconnections

- Reconfigurable cryptoprocessor

9

(No Transcript)