A Strange Counter - PowerPoint PPT Presentation

1 / 10

Title:

A Strange Counter

Description:

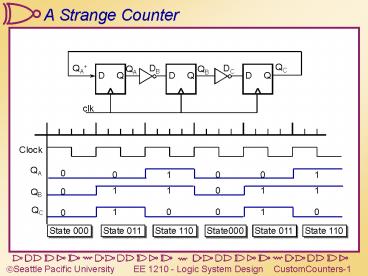

QC DB DC QA+ QA QB D Q D Q D Q clk Clock QA 0 1 0 0 0 1 1 1 0 1 1 0 QB QC 0 1 0 1 0 0 State 110 State 000 State 011 State 011 State 110 State000 A Strange Counter ... – PowerPoint PPT presentation

Number of Views:85

Avg rating:3.0/5.0

Title: A Strange Counter

1

A Strange Counter

2

A Strange Counter (Redrawn)

CombinationalFeedback Logic

DA

QA

D

Q

NextState

DB

QB

CurrentState (Output)

D

Q

DC

QC

D

Q

clk

3

A Generalized Synchronous Circuit

NextState

Outputs may be The state itself Some function of

the state

The number of possible states is 2n, where n is

the number of FlipFlops.

4

Analyzing a counter

QAQBQC

001

000

011

010

110

101

111

100

5

Custom Counters

Step 2 State Transition Table

Note the Don't Care conditions

6

Custom Counter Mapping to D FFs

Step 3 Choose Flipflop Type for Implementation

Figure out FF inputs that will cause

appropriate state change

For D FFs next state is just the D input Q ? D

Next State Functions with D FFs

7

Custom Counter Finishing

Step 4 Make K-maps for each flipflop input and

find final functions

DBABC AC

DAAC BC

DC C

8

Custom Counter Remapping to T FFs

Step 3 Choose Flipflop Type for Implementation

Figure out FF inputs that will cause

appropriate state change

1

1

0

For T FFs, we have to look at the current state

and the next.If the next state is different from

the current, then we must toggle (T1).

Next State Functions with T FFs

9

Finishing with Toggle FFs

Step 4 Make K-maps for each flipflop input and

find final functions

TB AC B AC

TAC(AB)

TC1

10

VHDL Counters

LIBRARY ieee USE ieee.std_logic_1164.all ENTITY

cnt IS PORT(clk IN STD_LOGIC reset IN

STD_LOGIC z OUT STD_LOGIC_VECTOR(2 downto

0)) END cnt

ARCHITECTURE behavior OF cnt IS Type state_type

is (A,B,C,D,E,F) SIGNAL state

state_typeBEGIN PROCESS(reset,clk) BEGIN if

(reset1) then state lt A z

lt000 elsif (rising_edge(clk))then case

state is when Agt state lt B z lt

"011" when Bgt state lt C z lt

100" when Cgt state lt D z lt

"101" when Dgt state lt E z lt

010" when Egt state lt F z lt

001" when Fgt state lt A z lt "000" END

CASE end if end process END behavior

Declare possible states (A-F is six states)

Asynchronous reset to 000

Heres the counter