Trigger and DAQ System - PowerPoint PPT Presentation

Title:

Trigger and DAQ System

Description:

EmC trigger makes a sum of 24 Crystal signals to form a trigger cell uses trigger cells to make ... Parallel Computing Readout from VME Easy to Upgrade and Port ... – PowerPoint PPT presentation

Number of Views:112

Avg rating:3.0/5.0

Title: Trigger and DAQ System

1

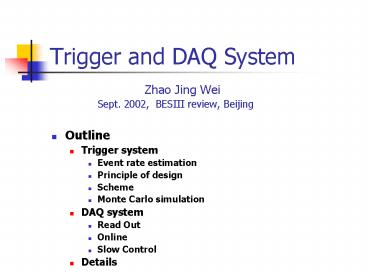

Trigger and DAQ System

- Zhao Jing Wei

- Sept. 2002, BESIII review, Beijing

- Outline

- Trigger system

- Event rate estimation

- Principle of design

- Scheme

- Monte Carlo simulation

- DAQ system

- Read Out

- Online

- Slow Control

- Details

2

Trigger System __ Estimation of event rate

- Purpose

- To select all interested events for physics from

backgrounds - To suppress background as possible

- Event rate after Level 1 can be sustainable for

DAQ system

3

Trigger System__ Estimation of event rate

- Total trigger rate

- good event rate (2000, LBEPCII 1 ? 1033

cm-2 s-1) - bhabha rate (800,to be pre-scaled)

- cosmic event rate (lt200,from 1500)

- beam background rate (lt2000Hz,from

13MHz) - 4000 Hz

4

Trigger System__ Estimation of event rate

Backgrounds rate vs beam current At BESII/BEPC

5

Trigger System__Principle

- Challenges to BESIII trigger design

- High good event

- High Backgrounds

- Multi-bunches93, small bunch spacing8ns

- No dead time design in trigger system

- Pipeline processing must be used

- (Latch-process-decision mode not possible in

8ns) - Latency of trigger signal necessary

6

Trigger System__Principle

- Hardware trigger software trigger(filter)

- FEE signal is splitted to

- trigger FEE pipeline

- L1 signal 3.2 ?s latency

- FEE pipeline clock 40MHz

- FEE Control Logic checks L1 with FEE pipeline

clock - L1 YES

- moves pipeline buffer data

- L1 No

- overwritten by new data

7

Block Diagram of BES III Trigger

Global Trigger Logic

TOF

DISC

Hit/Seg Count

Track Match

MDC

DISC

Track Seg. Finder

Track Finder

Energy Balance

EMC

TrigSum

TC Sum

Etotal Sum

L1P

Cluster Counting

MU

DISC

Mu track

CLOCK

RF

TTC

3.2 ?s

8

Trigger System__Scheme

- One way of the detector signal from FEE is sent

to trigger system. - TOF trigger

- hit, time and topology information

- MDC trigger

- checks for a track segment

- looks for a track with track segments

- counts the number of tracks.

- EmC trigger

- makes a sum of 24 Crystal signals to form a

trigger cell - uses trigger cells to make energy balance

9

Trigger System__Scheme

- Track match

- The messages from TOF, EmC, MDC will be used in

track Matching to check whether there are matched

tracks. - Global trigger

- All messages will be sent to global trigger,

based on trigger conditions if the event is good

is determined. - Level 1 signal

- Global trigger will send L1 signal to readout

modules of electronics if it is good event.

10

MDC trigger schemes

GLT

- Scheme A(AX only)

- TSF TF TRKCNT

- Scheme B(AXST)

- TSF GTSF BLTPTDTRKCNT

11

MDC trigger simulation

- Feasibility of trigger scheme study

- Trigger efficiency study

- Wire in-efficiency influence study

- Backgrounds rejecting ability study

- Production of configuration data

- Track Segment Finding

- Track Finding/PTD

12

Trigger efficiency vs Pt and wire efficiency

Configuration Pt gt 120 MeV

TSFNcomb8

TSFNcomb24

tracks with Ptgt130MeV Weffgt95 TrigEffgt95

13

BESIII EMC trigger scheme

FEE 8ch sum

Gain Adj.

14

EMC Simulation

- lt20 difference acceptable

- Gain adjustment for each crystalPDPreAmp chain

- Trigger Cell should be at least 4X4 16 crystals.

- 4X624 is taken

15

Summary of Trigger System

- Hardware trigger software filter

- L1 latency 3.2 ?s

- Pipeline clock 40 MHz

- Monte Carlo simulation going well

- backgrounds, MDC, EMC trigger schemes

- Design scheme drafted

- Some modules designed/designing

- Further/detailed designing undergoing

16

BESIII DAQ system__Tasks

- Event readout from FEE

- Event building

- (fragments ? sub-events ? a full event)

- Online event filtering

- (L3 trigger, 50 backgrounds suppressed)

- Event recording to persistent media

- Run control of DAQ system

- Monitoring (event, histogram display ...)

- Message reporting functions

17

Data Rate Estimation

18

Data Volume Estimation

- Electronic Channels to be Readout 40K(30K TDC

plus ADC) - Level-1 Trigger Rate 4KHz (2KHz Good Events)

- Event Size 12KBytes

- Data rate after Level 1 will be 49MByte/sec

- Data rate to be recorded on tape 37MByte/sec

- 1000 times than BESII DAQ System(0.04MByte/sec)

- Data volume will be 240TByte/5year

19

Technologies Challenges

- Multi-level Buffering(module,crate,PC)

- Switch Network(Gigabit)

- Parallel Computing

- Readout from VME

- Easy to Upgrade and Port

- Data/Message storage and good management

- Database is needed.

- System integration Easy to operating

- Software Engineering guarantee good quality

20

Readout Scheme

21

Readout RD and Result

- Test for VME bus and Network

- 3MByte/sec for programming I/O

- 13MByte/sec for DMA

- 100M Network is OK, it is possible that VME bus

readout will be a