Trending ACD performance - PowerPoint PPT Presentation

1 / 12

Title:

Trending ACD performance

Description:

Using veto settings and zero suppression values from veto scan done on 04/26 ... Two of the subsets were taken with the LAT on its side ... – PowerPoint PPT presentation

Number of Views:31

Avg rating:3.0/5.0

Title: Trending ACD performance

1

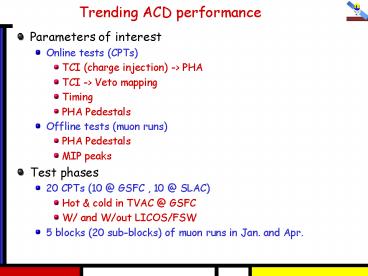

Trending ACD performance

- Parameters of interest

- Online tests (CPTs)

- TCI (charge injection) -gt PHA

- TCI -gt Veto mapping

- Timing

- PHA Pedestals

- Offline tests (muon runs)

- PHA Pedestals

- MIP peaks

- Test phases

- 20 CPTs (10 _at_ GSFC , 10 _at_ SLAC)

- Hot cold in TVAC _at_ GSFC

- W/ and W/out LICOS/FSW

- 5 blocks (20 sub-blocks) of muon runs in Jan. and

Apr.

2

CPT Test Phases

- At GSFC (08/05 09/05)

- Reference (not shown)

- PostVibe (1)

- Cold_1, Cold_2, Hot_2, Cold_3, Hot_3, Cold_4

(2-7) - tvac_ambient, tvac_dooropen (8-9)

- At SLAC

- Pre-install (09/05) (off LAT, EM GASU) (10)

- Lat_1, Lat_2 (12/05) (11-12)

- Voltage drop b/c of Veto driver issue

- Licos (13-19)

- Various timing changes

- Hitmap delay (5?16), hold delay, trg_seq (80?89)

- Test point 13 was actually done with LATTE, but

with LICOS-style scripts - The TCI-strobe, poll trigger sequence is

different from LATTE

3

Pedestal from online script

One Entry Per PMT

GSFC

SLAC

TVAC

LICOS/FSW (April 06)

LATTE (05)

In SLAC runs outliers are all from GAFE

17 channels

Zero suppress is Set at 15 counts

4

Hitmap Latching Delay

One Entry Per PMT

GSFC

SLAC

TVAC

LICOS/FSW (April 06)

LATTE (05)

Changing trg_seq from 80 to 89 caused a

corresponding 9 count shift in the

optimal hitmap_delay (delay before latching

the discriminator status)

5

Front End Hold Delay Timing

One Entry Per GARC

GSFC

SLAC

TVAC

LICOS/FSW (April 06)

LATTE (05)

The values at -35 are null values from a failed

test. Otherwise this just reflect the change in

trg_seq There is more scatter than hitmap

delay b/c this is the analog hold time

6

TCI to PHA mapping

One Entry Per GARC

GSFC

SLAC

TVAC

LICOS/FSW (April 06)

LATTE (05)

Need to confirm that effects in TP 13-14 come

from new strobe-poll sequence that they were

corrected by the trg_seq change

7

TCI Linearity Noise

One Entry Per PMT

GSFC

SLAC

TVAC

LICOS/FSW (April 06)

LATTE (05)

Moving from ACD-only to full LAT seems to have

increased the noise in the TCI runs and slightly

affected the goodness of fit

This is just more scatter in the points, not

non-linearity

8

TCI to Veto Mapping

One Entry Per PMT

GSFC

SLAC

TVAC

LICOS/FSW (April 06)

LATTE (05)

Many channels changed about 8-10 with LICOS

(also changed hitmap_delay)

The NA channels changed by up to 50

9

Muon Run Test Phases

- Reference is Jan. SVAC runs

- Block 1 (04/04 04/18)

- Both Veto Drivers Enabled -gt small Voltage sag _at_

FE (3.2V) - 10 sub-blocks of 10-25 runs ( 10 M events)

each - LAT-7xx and B-31 runs

- Block 2 (04/20 04/26)

- Single set of Veto Drivers -gt FE voltages close

to nominal (3.3V) - 8 sub-blocks

- LAT-7xx runs

- Block 3 (04/27 present)

- Using veto settings and zero suppression values

from veto scan done on 04/26 - 2 sub-blocks as of 04/28

- Sub-block 1 is ACD triggered.

10

PHA Pedestals from muon runs

One Entry Per PMT

Reference is Jan. SVAC B-13 runs

The first block of muon runs were taken with

both sets of veto drivers enables. This caused a

voltage sag which affected the pedestals, esp. on

the GAFE 17 channels

11

Muon Peak positions

One Entry Per PMT

Block 1

Block2

Block3

Two of the subsets were taken with the LAT on its

side Many of the tiles had limited statistics

poorer fits

One subset was taken w/ the ACD only allowed to

trigger the LAT. Tiles not used in the trigger

have low statistics poor fits

12

Summary

- Tools in place to trend ACD performance

- All basic quantities being tracked

- Some cross checks should be implemented

- Online v. Offline Pedestals, Veto Offset, Slope

- Most features of trending analysis understood

- Hitmap Hold timing ok

- Pedestals ok, both online offline

- Depended on Voltage _at_ FE

- TCI ? PHA mapping ok

- Depended on trg_seq setting

- TCI linearity got worse on LAT, but steady since

install - TCI ? Veto mapping changed w/ LICOS / FSW runs

- Still need to understand this

- Muon MIP peaks very steady