Final Review 1 - PowerPoint PPT Presentation

1 / 26

Title:

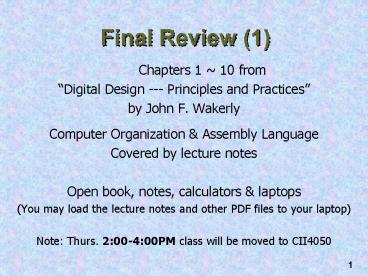

Final Review 1

Description:

Open book, notes, calculators & laptops (You may load the lecture notes and other PDF files to your laptop) ... Switching Algebra. Karnaugh Map. Sum-of-Product, ... – PowerPoint PPT presentation

Number of Views:32

Avg rating:3.0/5.0

Title: Final Review 1

1

Final Review (1)

- Chapters 1 10 from

- Digital Design --- Principles and Practices

- by John F. Wakerly

- Computer Organization Assembly Language

- Covered by lecture notes

- Open book, notes, calculators laptops

- (You may load the lecture notes and other PDF

files to your laptop) - Note Thurs. 200-400PM class will be moved to

CII4050

2

Representative Problems from Midterm 1 2

- Number systems

- Combinational-Circuit Principles

- Basic Sequential Circuit Elements

- State Machine Analysis Design

3

Prob.1 How many bits would each of the following

decimal numbers take to represent in binary

(unsigned)? (midterm 1)

- 1000

- 100000

10

29512lt 1000 lt 1024210

Prob.2 What is the legal range of 12-bit 2s

complement numbers? (midterm 1)

Fact N-bit 2s complement number range -2N-1 to

2N-1-1

-211-2048 to 211-12047

4

Prob.3 Extend these 4-bit 2s complement

numbers to 8-bits. (midterm 1)

- 0100

- 1111

- 1010

00000100 11111111 11111010

Prob.4 Negate these 4-bit 2s complement

number. (midterm 1)

- 0100

- 1111

- 1010

1100 0001 0110

Fact first flip each bit, then add 1

5

Combinational-Circuit Principles

- Switching Algebra

- Karnaugh Map

- Sum-of-Product, Product-of-Sum

6

Prob.5 Simplify the following boolean

expressions. (midterm 1)

- F AAB

- F (ABC) (AB) (AC)

F AAB AA1A(1B) A(1B) AB

AABAB A(AA)B A B

F (ABC) (AB) (AC) ABC

AB AC

Refer to K-Map

A

7

Prob.6 Consider the following truth table.

(midterm 1)

a. Write F in SOP form

b. Write F as a boolean function in canonical SOP

notation

F ABCD ABCD ABCD ABCD

ABCD ABCD ABCD ABCD

8

c. Write F in POS form

d. Write F as a boolean function in canonical POS

notation

F (ABCD) (ABCD) (ABCD)

(ABCD) (ABCD) (ABCD)

(ABCD) (ABCD)

9

e. Write the values into K-map

f. Find the optimal expression

F BD BD

10

Basic Sequential Circuit Elements

- Latches and Flip-Flops

- Latches R-S, D

- Flip-flops D, J-K, T

- Terms set-up time, hold time, positive/negative

edge triggered - Registers

- Counters

11

Use NOR gates to substitute the four NAND gates

(midterm 2)

12

R

S

13

Prob. 8. Given the following sequential circuit,

where the flip-flops have worst-case setup times

of 20 ns, hold times of 10 ns, and propagation

delays of 15 ns. Assuming combinational logic has

a worst-case delay of 75 ns, what is the maximum

allowable frequency of the clock? (midterm 2)

75ns20ns15ns110ns ? 9.09 MHz

14

- Prob. 9. An UV flip-flop has four operations

complement, set to 1, clear to 0, and no change,

when inputs U and V are 00, 01, 10, and 11,

respectively. (midterm 2) - Derive the characteristic equation.

- Show how the UV flip-flop can be converted to a

T flip-flop

15

Function table

Q QV QU

16

b. Show how the UV flip-flop can be converted to

a T flip-flop.

UT, VT

17

Prob. 10. Design a counter based on the counter

74x163 as shown here to achieve the counting

sequence 0, 1, 2, ... , 15, 12, 13, 14, 15, 0,

1, 2, ... , 15, 12, 13, 14, 15, 0, 1, 2,...

(Note Q0 is LSB and Q3 is MSB, this counting

sequence repeats every 20 clock cycles). (midterm

2)

- In one counting sequence

- Load 12 after counting to 1st 15

- Go to 0 after counting to 2nd 15

Load 12 every other the event of counting to 15

18

(No Transcript)

19

State Machine Analysis Design

- Moore machine configuration

- output depends only on state

- Mealy machine configuration

- output depends on state inputs

- State machine analysis

- State machine design

20

Prob. 11. Analyze the following clocked

synchronous state machine (a) write transition

equation, (b) write state/output table (use names

S0 S3 for Q0 Q100 11), and (c) draw the

state diagram. (midterm 2)

J

En

k

- En Q1, J X Q0, K X

- Q0 EnQ0 EnQ0 Q1 JQ1 KQ1

- Q1Q0 Q1Q0 XQ1 Q0Q1

XQ1

21

Q0 Q1Q0 Q1Q0, Q1 XQ1 Q0Q1

XQ1 Z Q1 XOR Q0

S0 S3 for Q0 Q100 11

22

(No Transcript)

23

Prob. 12. Design a Mealy machine that has one

input X and one output Z. The output Z1 if and

only if the total number of 1s received is

divisible by 3 (for example, 0, 3, 6, 9, ).

The number of received 1s, N, always falls into

three scenarios

3m ? S0 3m1 ? S1 3m2 ? S2

24

Let S0 ? 00, S1 ? 01, S2 ? 10

25

Use D Flip-Flop

D0Q1XQ0X

For Q0D0

26

D1Q1XQ0Q1X

For Q1D1

ZQ0Q1XQ0X

For Z

Finally, draw the circuit!