Layout - PowerPoint PPT Presentation

1 / 63

Title:

Layout

Description:

Mid band frequency equal to wo= 45MHz 10%. The ... MP5. MN4. MN3. MN7. MN2. MN5. MN6. MN1. Bias circuit Layout. 8/2/09. 47. G. D. S. B. B. S. D. S. D. G ... – PowerPoint PPT presentation

Number of Views:31

Avg rating:3.0/5.0

Title: Layout

1

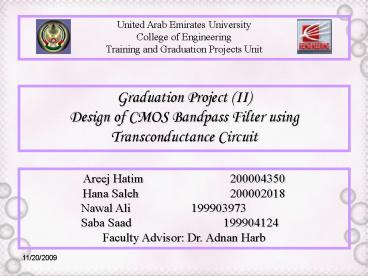

United Arab Emirates UniversityCollege of

EngineeringTraining and Graduation Projects Unit

Graduation Project (II)Design of CMOS Bandpass

Filter using Transconductance Circuit

Areej Hatim 200004350 Hana Saleh 200002018

Nawal Ali 199903973 Saba

Saad

199904124 Faculty Advisor Dr. Adnan Harb

2

Outline

- Introduction.

- Analog IC design flow.

- Transconductance circuit.

- Modify Transconductance circuit.

- Common mode feed back.

- Transconductance circuit characteristics.

- Biquad Band pass filter.

- Biquad Band pass filter charactristics.

- Layout.

- Project Cost.

- Cleanroom.

- Conclusion.

3

(No Transcript)

4

Filter Specifications

- Frequency bandwidth of 10MHz 80MHz.

- Transfer function

- Mid band frequency equal to wo 45MHz 10.

- The linearity must be better than 41 dB.

5

Analog IC Design Flow

6

(No Transcript)

7

Transconductance (Gm) circuit

- Transfer function Vout/Vin Gm/sC

- Unity gain frequency wo Gm/C

- wo 45 MHz

8

AC simulation

9

Gm circuit Modification

New Gm circuit

Old Gm circuit

10

Small signal equivalent circuit for new Gm

11

Bias Circuit

- First step

12

- Second step

13

- Third step

I2I32I1 I4I5 I1/3

14

Gain vs. Frequency

15

CMFB Circuit

16

(No Transcript)

17

Gm-C circuit characteristics

- Frequency response.

- Gain tunability.

- Linearity.

- Power consumption.

18

Frequency response vs.Vref

19

- At T -40oC

- When Vref (750mV-900mV) the range of Freq.

7.1MHz to 108MHz. - At T 125oC

- When Vref (860mV-900mV) the range of Freq.

41.2MHz to 54MHz. - The simulation shows that at all temperature, the

Gm can be tuned to meet wo 45 MHz.

20

Tunability

Gain Vout / Vin

21

Linearity Characteristic

- Effect of frequency.

- Effect of reference voltage.

- Effect of Temperature.

- Effect of output voltage.

22

Effect of Frequency

23

Effect of Vref

24

Effect of Temperature

25

Effect of output voltage

26

Power consumption

- P (Vdd Vss)I 5.4mW

Vdd

Vss

27

Biquad Band Pass Filter circuit

28

Bias circuit

29

BBPF circuit characteristics

- Frequency Response and Tunability

- Linearity Characteristics

- Power Consumption

30

Frequency Response Tunability

Vref 0.908 V, Freq. 45MHz, T27oC

31

Value of reference voltage at the mid band

frequency

32

Linearity Characteristics

- Effect of Frequency

- 30MHz, 45 10 MHz, 60MHz.

- Effect of Temperature

- -40oC, 27oC, 125oC.

- Effect of output voltage

33

Effect of Frequency

34

Effect of Temperature

35

Effect of Output Voltage

36

Power Consumption

- Minimize power by using One Bias circuit in the

BBPF circuit so

37

Layout

- Used Technology Specifications.

- Transistors Sizing.

- Bias Circuit Gm Circuit.

- Bulk Terminal Connection.

- Capacitor Calculation.

- Layout vs. Schematic (LVS).

- Biquad Band Pass Filter Connection.

- Design Rule Check (DRC).

38

Used Technology Specifications

39

(No Transcript)

40

Technology Specifications

- In this technology 1? 0.2µm.

- The maximum dimension 100 ?

41

Transistor Sizing

42

Bias circuit Transistors Sizing

43

Bias circuit Transistors Sizing

44

Gm Transistors Sizing

45

Gm tansconductance Layout

46

Bias circuit Layout

47

Bulk Terminal Connection

48

(No Transcript)

49

P-MOS

VDD

50

N-MOS

Vss

51

Capacitor Calculations

- Designed Capacitor Structure.

- Capacitor sizing calculations

52

Layout vs Schematic (LVS)

Gm LVS

53

Bias Circuit LVS

54

Biquad Band Pass Filter Connection

Gm Circuits

Bias Circuit

Capacitor

55

Design Rule Check (DRC)

- Width rules.

- Width of poly wire.

- Spacing rules.

- Spacing of two poly wires.

- Enclosure rules.

- Enclosure between a wall and a source/ drain

active. - Extension rules.

- Gate extension

56

Design Rule Check

57

Project Cost

- Designing Cost

- Engineer payment 20000 for each engineer.

- The total 80000.

- Software (OrCAD) for designing the circuit

- The cost 9995

- Software (Electric) for make layout for the

circuit - The cost 49

58

- Implementation cost

- Fabrication cost

- 13800/40 copies of our circuit.

- Packaging cost

- The cost 40 per chip.

- To package the 40 chips, the price will be 4040

1600 - Testing Cost

- DRC (Design Rule Check)

- The cost 500 .

- Test and documentation

- The cost 1800.

- Total Cost 107,44 which is also known as

capital cost.

59

Cleanroom

- Dangers

- Safety and Protocol

60

Dangers in Cleanroom

61

Safety and Protocol

- Personal Protective

- Equipment (PPE)

- Fire Safety

- First Aid

- The NFPA Diamond

- Gowning

- Chemical Product

- Emergency Contact

- Housekeeping and Cleanroom

Etiquettey - Material Data Safety Sheets (MSDS)

- Cleanroom Procedures

62

Conclusion

- What have we gained?

- Faced problems.

- This project will be a part of a conference paper.

63

,

Thanks for attention