FPGA QR Performance Comparison - PowerPoint PPT Presentation

1 / 1

Title:

FPGA QR Performance Comparison

Description:

FPGA QR Performance Comparison. Dr. John McAllister. Programmable Systems ... Mantissa length. Size. FPGA measurements based on Xilinx Virtex-II 6000 FPGA. ... – PowerPoint PPT presentation

Number of Views:55

Avg rating:3.0/5.0

Title: FPGA QR Performance Comparison

1

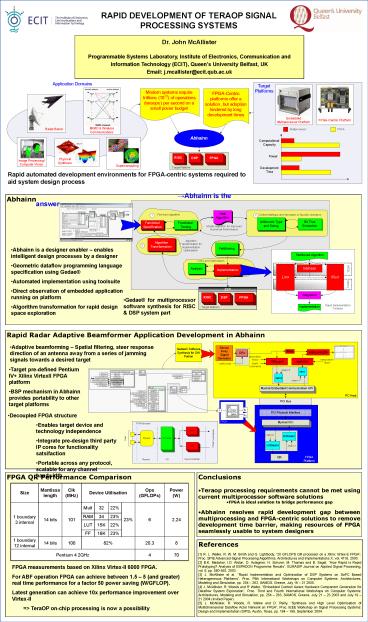

RAPID DEVELOPMENT OF TERAOP SIGNAL PROCESSING

SYSTEMS

Dr. John McAllister Programmable Systems

Laboratory, Institute of Electronics,

Communication and Information Technology (ECIT),

Queens University Belfast, UKEmail

j.mcallister_at_ecit.qub.ac.uk

Rapid automated development environments for

FPGA-centric systems required to aid system

design process ?Abhainn is the answer

Abhainn

- Abhainn is a designer enabler enables

intelligent design processes by a designer - Geometric dataflow programming language

specification using Gedae - Automated implementation using toolsuite

- Direct observation of embedded application

running on platform - Algorithm transformation for rapid design space

exploration

- Gedae for multiprocessor software synthesis for

RISC DSP system part

Rapid Radar Adaptive Beamformer Application

Development in Abhainn

- Adaptive beamforming Spatial filtering, steer

response direction of an antenna away from a

series of jamming signals towards a desired target

- Target pre-defined Pentium IV Xilinx VirtexII

FPGA platform - BSP mechanism in Abhainn provides portability to

other target platforms

- Decoupled FPGA structure

- Enables target device and technology independence

- Integrate pre-design third party IP cores for

functionality satsifaction - Portable across any protocol, scalable for any

channel bandwidth

FPGA QR Performance Comparison

- Conclusions

- Teraop processing requirements cannot be met

using current multiprocessor software solutions - FPGA is ideal solution to bridge performance gap

- Abhainn resolves rapid development gap between

multiprocessing and FPGA-centric solutions to

remove development time barrier, making resources

of FPGA seamlessly usable to system designers

References 1 R. L. Walke, R. W. M. Smith and

G. Lightbody, 20 GFLOPS QR processor on a Xilinx

Virtex-E FPGA, Proc. SPIE Advanced Signal

Processing Algorithms, Architectures and

Implementations X, vol. 4116, 2000. 2 B.K.

Madahar, I.D. Alston, D. Aulagnier, H. Schurer,

M. Thomas and B. Saget, How Rapid is Rapid

Prototyping? Analysis of ESPADON Programme

Results, EURASIP Journal on Applied Signal

Processing, vol. 6, pp. 580-593, 2003. 3 J.

McAllister et al. Rapid Implementation and

Optimisation of DSP Systems on SoPC Based

Heterogeneous Platforms, Proc. Ffith

International Workshops on Computer Systems

Architectures, Modeling and Simulation, pp. 254

263, SAMOS, Greece, July 19 21 2005. 4 J.

McAllister, R. Woods and R Walke, Embedded

Context Aware Hardware Component Generation for

Dataflow System Exploration, Proc. Third and

Fourth International Workshops on Computer

Systems Architectures, Modeling and Simulation,

pp. 254 263, SAMOS, Greece, July 21 23 2003

and July 19 21 2004 (Invited Paper). 5 J.

McAllister, R. Woods, R. Walke and D. Reilly,

Synthesis and High Level Optimisation of

Multidimensional Dataflow Actor Network on FPGA,

Proc. IEEE Workshop on Signal Processing Systems

Design and Implementation (SIPS), Austin, Texas,

pp. 164 169, September 2004.

FPGA measurements based on Xilinx Virtex-II 6000

FPGA. For ABF operation FPGA can achieve between

1.5 5 (and greater) real time performance for a

factor 50 power saving (W/GFLOP). Latest

generation can achieve 10x performance

improvement over Virtex-II gt TeraOP on-chip

processing is now a possibility