3D ICs: Processing and Integration Protocols - PowerPoint PPT Presentation

1 / 19

Title:

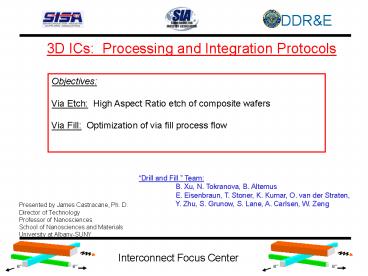

3D ICs: Processing and Integration Protocols

Description:

... 3 f ff fff3f3 33 3f333 f3 f 3 f 3 f 3 f f ... 3f f ff fff3ff f f f ff 3f ff ffff fffff3fff3 f3f3 f3ff33f3f ff fff3f3 3 3 3 ... – PowerPoint PPT presentation

Number of Views:29

Avg rating:3.0/5.0

Title: 3D ICs: Processing and Integration Protocols

1

3D ICs Processing and Integration Protocols

Drill and Fill Team B. Xu, N. Tokranova, B.

Altemus E. Eisenbraun, T. Stoner, K. Kumar, O.

van der Straten, Y. Zhu, S. Grunow, S. Lane, A.

Carlsen, W. Zeng

Presented by James Castracane, Ph. D. Director of

Technology Professor of Nanosciences School of

Nanosciences and Materials University at

Albany-SUNY

2

3D Silicon Devices The Face-to-Face Bonded

Approach

The Face-to-Face Bonding Strategy

Demonstration of Feasibility Tasks Deliverables

Design of Multi-level 3D Device Scheme.

Predictive Modeling of Reliability and

Performance. Identification of

multi-level 3D

Demonstration Test Vehicle.

Development and Implementation of

Optimized Fabrication Flow. Structural,

Chemical, Reliability and Electrical

Characterization of Test Vehicle.

Comparative Assessment of Performance of

3D Test vehicle versus 2D Analog.

(Face to Face stacking permits thinner top CMP

after bonding)

3

High Aspect Ratio Fabrication for 3D Structures

Plasma Therm Versalock 700 ICP Etcher w/Bosch

Process

Through Wafer Etching for 3D Interconnects HAR

Structures for MEMS

Etch Rate 2- 4 m/min (Si) 0.2 m/min

(oxide) SiSiO2 gt1501 SiPhotoresist

gt751 Wafer Temp 25 C Sidewall Profile

Adjustable

Silicon Module Fully Operational

Oxide/Nitride Module Fully Operational

4

Customized Process Tools for 3D Tasks

Electronic Visions 200 mm Wafer Aligner

Electronic Visions 200 mm Wafer Bonder

5

The Face-to-Face Bonded 3D-Device

Approach Representative Milestone Very High

Aspect Ratio Through Etching of Stacked Wafers

Etch Rate 4 ?m/min SiSiO2 gt1501 SiPhotoresi

st gt751 Wafer Temp 25 oC Sidewall Profile

Adjustable

Expanded View

Note Scalloping

6

Continued HAR Etching Experiments

HAR Test Array

Controlled Sidewall Etch Sample

7

SEM Metrology of Bosch Process Etched Samples

Trench Example

Through Wafer Sample

8

Via Test Patterns

9

High Aspect Ratio Via Etch Tests

200 mm capable Si Tool Bosch etching 3D

Integration via Pattern

4 micron via

2 micron via

Aspect Ratio 15-201

10

High Aspect Ratio Via Etch Tests (cont.)

200 mm capable Si Tool Bosch etching 3D

Integration via Pattern

2 and 1 micron vias in Silicon

11

Oxide/nitride etch results

CF4 etch with low (200 W) power (40 minute

process)

12

Oxide/nitride etch results (cont.)

35 minute etch

85 minute etch

CHF3 etch with low (250W) power

13

High-Aspect-Ratio Via Etch/Fill through

Multi-Layers

Test wafer structure consists of different

materials, such as SiO2, SiNx, Glue, Si and

other low-k interlevel dielectrics

14

Initial FLARE Etching Experiments Metrology

Surface Profiling using KLA/TENCOR UV 1080 on

200 mm wafers

FLARE on Si

FLARE on SiO2 and Si

15

Initial FLARE Etching Experiments

FLARE on SiPatterned with Al Etched in

Plasmatherm Tool

16

High Aspect Ratio 200-mm Wafer Thin Film

Processing for 3D Structures

- Stand-alone tools

- CVD/ALD TiN, TaN

- CVD TiSiN, TaSiN

- MRC (TEL) Phoenix CVD cluster tool

- MOCVD WNx

- MOCVD Cu

- Varian MB2 PVD/CVD/ALD cluster tool

- PVD TiN, TaN

- MOCVD/MOALD Cu

Copper ECD tool

17

The Face-to-Face Bonded 3D-Device

Approach Representative Milestone Very High

Aspect Ratio Via/Trench Fill

Develop and optimize electrically reliable,

structurally robust, and fully- integrated fill

processes for very high aspect ratio vias and

trenches. Solutions are compatible with

semiconductor fabrication flows.

0.10?m

100nm

100nm

CVD TaN

CVD Cu

18

High Aspect Ratio Processing

Develop and optimize electrically reliable,

structurally robust, fully- integrated etch,

liner, and fill processes for very high aspect

ratio structures. Solutions are compatible with

200-mm wafer semiconductor fabrication flows.

100 nm

100nm

MOCVD WNx

ECD Cu

100nm

Current Barrier Layer Thickness Range 10-50

Angstroms

ALD TaNx

19

Conclusions and Next Steps

-- Basic process steps have been established --

High aspect ratio etching has been demonstrated

for Si and oxide/nitride stacks --

Excellent conformality of barrier layers has been

achieved with several deposition methods

including ALD -- High quality via and trench

fill has been accomplished -- Composite stack

etching is next step to be followed by

multi-wafer test vehicle