LeakSIS : Leakage Centric Physical Synthesis Methodology - PowerPoint PPT Presentation

1 / 1

Title:

LeakSIS : Leakage Centric Physical Synthesis Methodology

Description:

Department of Electrical and Computer Engineering, University of Maryland, College Park. ... Fabricate all devices using high Vth for low leakage in standby mode ... – PowerPoint PPT presentation

Number of Views:36

Avg rating:3.0/5.0

Title: LeakSIS : Leakage Centric Physical Synthesis Methodology

1

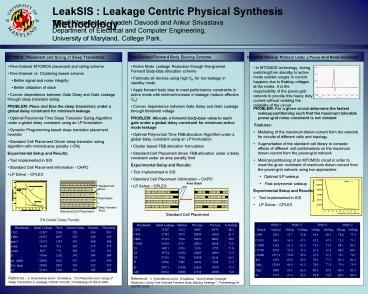

LeakSIS Leakage Centric Physical Synthesis

Methodology

Vishal Khandelwal, Azadeh Davoodi and Ankur

Srivastava Department of Electrical and Computer

Engineering, University of Maryland, College Park.

MTCMOS Placement and Sizing of Sleep Transistors

MTCMOS Wakeup Protocol Under a Power-Grid Noise

Constraint

- Fine-Grained MTCMOS placement and sizing scheme

- Fine-Grained vs. Clustering based scheme

- Better signal and noise integrity

- Better utilization of slack

- Convex dependence between Gate Delay and Gate

Leakage through sleep transistor sizing - PROBLEM Place and Size the sleep transistors

under a global delay constraint for minimum

leakage - Optimal Polynomial Time Sleep Transistor Sizing

Algorithm under a global delay constraint using

an LP formulation - Dynamic Programming based sleep transistor

placement heuristic - Standard Cell Placement Driven sleep transistor

sizing algorithm with minimal area penalty (5) - Experimental Setup and Results

- Tool implemented in SIS

- Standard Cell Placement information - CAPO

- LP Solver - CPLEX

- Active Mode Leakage Reduction through

fine-grained Forward Body-Bias allocation scheme - Fabricate all devices using high Vth for low

leakage in standby mode - Apply forward body bias to meet performance

constraints in active mode with minimal increase

in leakage (reduce effective Vth) - Convex dependence between Gate Delay and Gate

Leakage through threshold voltage - PROBLEM Allocate a forward body-bias value to

each gate under a global delay constraint for

minimum active mode leakage - Optimal Polynomial Time FBB allocation Algorithm

under a global delay constraint using an LP

formulation - Cluster based FBB allocation formulation

- Standard-Cell Placement driven FBB allocation

under a delay constraint under an area penalty

limit - Experimental Setup and Results

- Tool implemented in SIS

- Standard Cell Placement information CAPO

- LP Solver - CPLEX

- In MTCMOS technology, during switching from

standby to active mode sudden surges in current

happens due to floating voltages at the nodes. It

is the responsibility of the power-grid network

to provide this heavy duty current without

violating the reliability of the circuit

- PROBLEM For a given circuit determine the

fastest wakeup partitioning such that the maximum

tolerable power-grid noise constraint is not

violated - Features

- Modeling of the maximum drawn-current from the

network for circuits of different cells and

topology - Augmentation of the standard cell library to

consider effects of different cell combinations

on the maximum drawn-current from the power-grid

network - Minimal partitioning of an MTCMOS circuit in

order to meet the given constraint of maximum

drawn-current from the power-grid network using

two approaches - Optimal ILP wakeup

- Fast polynomial wakeup

- Experimental Setup and Results

- Tool implemented in SIS

- LP Solver - CPLEX

Standard Cell Rows Dead Space Sleep Transistor

Rows

Standard Cell Placement

5 Global Delay Penalty

Reference V. Khandelwal and A. Srivastava, "On

Placement and Sizing of Sleep Transistors in

Leakage Critical Circuits", Proceedings of

IWLS-2004

Reference V. Khandelwal and A. Srivastava,

"Active Mode Leakage Reduction Using Fine-Grained

Forward Body Biasing Strategy ", Proceedings of

ISLPED-2004