10 Micrometer Design Rules - PowerPoint PPT Presentation

1 / 45

Title:

10 Micrometer Design Rules

Description:

Bare silicon. After silicon dioxide ... PAINT RESIST STRIP ETCH C1 BARE. FIND MINIMUM OXIDE THICKNESS TO MASK BORON DIFFUSION ... OXIDE ETCH C3 and C4 BARE ... – PowerPoint PPT presentation

Number of Views:204

Avg rating:3.0/5.0

Title: 10 Micrometer Design Rules

1

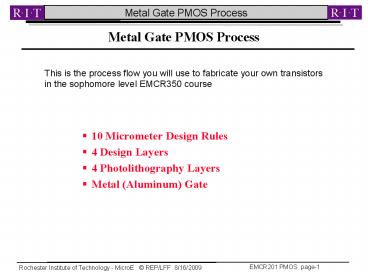

Metal Gate PMOS Process

This is the process flow you will use to

fabricate your own transistors in the sophomore

level EMCR350 course

- 10 Micrometer Design Rules

- 4 Design Layers

- 4 Photolithography Layers

- Metal (Aluminum) Gate

2

Process Flows

- Resistors

- Get wafer, scribe and clean

- Grow masking oxide

- Pattern for diffusion

- Etch masking oxide

- Strip resist

- Clean and spin on dopant

- Diffuse

- Strip off dopant source and masking oxide

- Grow new thick oxide

- Pattern for contact cuts

- Etch thick oxide

- Strip resist

- Deposit Aluminum

- Pattern for aluminum etch

- Etch Aluminum

PMOS Transistors Get wafer, scribe and

clean Grow masking oxide Pattern for

diffusion Etch masking oxide Strip resist Clean

and spin on dopant Diffuse Strip off dopant

source and masking oxide Grow new thick

oxide Pattern for thin (gate) oxide Grow gate

oxide Pattern for contact cuts Etch thick

oxide Strip resist Deposit Aluminum Pattern for

aluminum etch Etch Aluminum Strip resist Sinter

1

1

2

3

2

4

3

3

Design Rules

- The smallest a contact can be is one unit

(lambda, l) by one unit. - In this case lambda will be 10 microns

- Diffusion and metal have to extend at least one

unit around a contact - The gate oxide has to extend over a diffusion by

at least on unit

4

STARTING WAFER N-TYPE, 5 OHM-CM

Silicon

5

ID01 - Scribe Identification Code on the

WaferDE01 - Four Point Probe to Check

Resistivity

I

V

D1

L030924

6

OXIDE THICKNESS COLOR CHART

7

Dry Oxidation

(100) Si

(111) Si

1.0

1.0

1200C

1200C

1100C

1100C

1000C

1000C

900C

Oxide Thickness (mm)

Oxide Thickness (mm)

0.1

0.1

900C

800C

800C

0.01

0.01

0.1

0.1

10.0

1.0

10.0

1.0

Oxidation time in hours

Oxidation time in hours

8

Steam Oxidation

(111) Si

(100) Si

10

10

1

1

Oxide Thickness (mm)

1150C

1150C

Oxide Thickness (mm)

1200C

1200C

1100C

1050C

1100C

0.1

1050C

0.1

1000C

1000C

950C

950C

900C

850C

850C

900C

0.01

0.01

10.0

1.0

0.1

10.0

1.0

0.1

Oxidation time in hours

Oxidation time in hours

9

MINIMUM OXIDE THICKNESS FOR DIFFUSION MASKING

10

1200 C

1100

Phos.

1

1000

900

Xox , µm

1200

1100

10-1

Boron

1000

10-2

900

10-3

100

1,000

10

t, Time, (min)

10

RCA Clean then Grow 5000 Å Oxide

Push at 900 C in N2 Ramp to 1100 C in dry

O2 Start Soak at 1090 C Time 48 min. in

wet O2 Ramp down to 1000 C in N2 Pull at 1000 C

in N2

5000 Å SiO2

After silicon dioxide growth (should look

blue-green) It can be hard to tell under the

microscope

Bare silicon

11

STEP ETCH APPARATUS

Oxide

Plastic, right!

BUFFERED HF

Lower 1/4 inch every 30 seconds

12

ETCH STEPS IN OXIDE ON C1

4200 Å

3500 Å

2800 Å

2100 Å

1400 Å

700 Å

BARE SILICON

Top View

Side View

Actual colors are not this saturated

13

COAT WITH PHOTORESIST

1 µm Positive Photoresist

5000 Å SiO2

14

Expose with Mask Layer One Diffusion Openings

1x Mask

opaque

clear

Shadow

Ultra-Violet Radiation

positive photoresist

exposed areas develop away

SiO2

Silicon

15

ETCH OXIDE

Not drawn to the same scale horizontally as

vertically, the actual Cross-sectional view

should be 20-50 times wider.

16

STRIP RESIST and RCA CLEAN

17

After Patterning of Diffusion Masking Oxide

Silicon Dioxide

Bare Silicon

Diffusion openings (Bare Silicon)

18

SPIN-ON P-TYPE DOPANT

19

PRE-DEPOSIT, OXIDE ETCH and RCA CLEAN

rs1

Xj1

20

ETCH STEPS IN OXIDE ON C5FIND SLOW AND FAST ETCH

RATES

SiO2 Mask

Si

8000 Å

SLOW

FAST

BARE SILICON

After diffusion and step etch

Before Diffusion

21

PAINT RESIST STRIP ETCH C1 BAREFIND MINIMUM

OXIDE THICKNESS TO MASK BORON DIFFUSION

8000 Å

. V/I V/I V/I V/I V/I . . .

XXXX

BARE SILICON WITH SPIN-ON DOPANT

22

GROOVE and STAIN C2, FIND Xj1 AFTER PRE-DEPOSIT

Groove

Xj (N M) / D

D

M

N

After Stain

23

DE01 - FOUR POINT PROBE C1, C2, C3, C4FIND

SHEET RESISTANCE OF DIFFUSION AFTER PREDEPOSIT

I

V

ohms/square

24

FIELD OXIDE GROWTH (5000 Å)

Push at 900 C in N2 Ramp to 1100 C in dry

O2 Start Soak at 1090 C Time 48 min. in

wet O2 Ramp down to 1000 C in N2 Pull at 1000 C

in N2

Slightly Thicker Oxide Over Diffusion

25

After Field (Thick) Oxide Growth

Oxide over lightly doped silicon

- Oxide over heavily doped silicon

26

Photolithography, Mask Level 2 (define thin OXIDE

regions)

opaque

clear

Shadow

Ultra-Violet Radiation

27

Active (thin oxide) Area Etch and resist strip

28

After Patterning/Etching Masking SiO2 (before

Thin Gate SiO2 Growth)

- Note that text has been added to the design to

label devices, pads etc.

29

OXIDE ETCH C3 and C4 BARE

These wafers are used to find the intermediate

junction depths and sheet resistances as we go

through the process. Note that Xj2 is deeper than

Xj1.

rs2

Xj2

30

GROOVE and STAIN and 4PT PROBE C3

Groove

Xj (N M) / D

D

M

N

After Stain

V

I

ohms/square

31

ASH RESIST, CLEAN, GROW GATE OXIDE - 700 Å

Push at 900 C in N2 Ramp to 1100 C in dry

O2 Start Soak at 1090 C Time 50 min. in

dry O2 Ramp down to 1000 C in N2 Pull at 1000 C

in N2

SiO2

700 Å SiO2

32

After Thin Gate Oxide Growth (dark brown areas)

33

PHOTOLITHOGRAPHY MASK LEVEL 3 - CONTACT CUT

opaque

clear

Shadow

Shadow

Shadow

Shadow

SiO2

SiO2

34

OXIDE ETCH C4 BARE

rs3

Xj3

Xj3 is deeper than Xj2!

35

GROOVE and STAIN and 4PT PROBE C4

Groove

Xj (N M) / D

D

M

N

After Stain

V

I

ohms/square

36

CONTACT CUT ETCH

SiO2

SiO2

37

Photomicrograph after contact cut etch and resist

strip

Contact

Thin Oxide 700 Å

Thick Oxide

38

ASH RESIST, RCA CLEAN and SPUTTER ALUMINUM

Xal

rs aluminum

SiO2

SiO2

39

After Aluminum Deposition

- Note how reflective the aluminum is

Aluminum everywhere, Everything short circuited

40

PHOTOLITHOGRAPHY LEVEL 4 - METAL

opaque

clear

v

Shadow

SiO2

SiO2

41

ETCH ALUMINUM (40C Phosphoric Acid)

photoresist

Aluminum

SiO2

SiO2

Silicon

P-type

P-type

42

ASH RESIST

43

After Aluminum Etch and Resist Strip

- Electrical Probe Pads are now visible, pad

numbers were done in the diffusion layer

44

SINTER Improves Contacts and Threshold Voltage

Before Sinter

After Sinter

Reduce Contact Resistance

Native Oxide

Hydrogen, neutral region

Oxygen

SiO2

charge region

silicon atom that has Nothing to bond to

(missing electron)

Interface

Silicon Crystal

Reduce Surface States

45

Electrical TEST

X

D

S

D

CROSS-OVER

Aluminum

G

SOURCE

DRAIN

GATE

SiO2

SiO2

Silicon

PMOS TRANSISTOR