Rfrence un mot Xn dans le cache - PowerPoint PPT Presentation

Title:

Rfrence un mot Xn dans le cache

Description:

R f rence un mot Xn dans le cache. Recherche de Xn dans le cache ... Un emplacement dans le cache peut appartenir plusieurs emplacements m moire. ... – PowerPoint PPT presentation

Number of Views:63

Avg rating:3.0/5.0

Title: Rfrence un mot Xn dans le cache

1

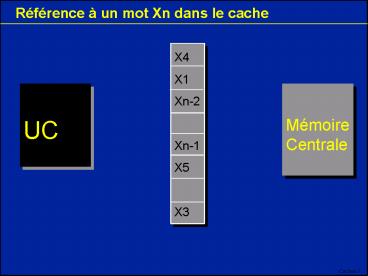

Référence à un mot Xn dans le cache

X4 X1 Xn-2 Xn-1 X5 X3

Mémoire Centrale

UC

2

Référence à un mot Xn dans le cache

X4 X1 Xn-2 Xn-1 X5 X3

Mémoire Centrale

UC

Xn

UC veut faire référence à Xn

3

Référence à un mot Xn dans le cache

X4 X1 Xn-2 Xn-1 X5 X3

Mémoire Centrale

UC

Xn

Recherche de Xn dans le cache

4

Référence à un mot Xn dans le cache

X4 X1 Xn-2 Xn-1 X5 X3

Mémoire Centrale

UC

Xn

Défaut de cache

Recherche de Xn dans le cache

5

Référence à un mot Xn dans le cache

X4 X1 Xn-2 Xn-1 X5 Xn X3

Mémoire Centrale

UC

Extraction de Xn dans la mémoire Insertion dans

le cache

6

Bilan Référence à un mot Xn

X4 X1 Xn-2 Xn-1 X5 Xn X3

X4 X1 Xn-2 Xn-1 X5 X3

Après la référence à Xn

Avant la référence à Xn

7

Questions à résoudre

- Question 1 Où placer un bloc?

- Question 2 Comment un bloc est-il trouvé ?

- Question 3 Quel bloc remplacé lors dun défaut

? - Question 4 Comment sont traités les écritures?

8

Question 1

- Où placer un bloc?

- Caches à correspondances directes

- Caches totalement associatifs

- Caches associatifs par ensemble

9

Les caches à correspondance directe

Le moyen le plus simple est dassigner un

emplacement unique dans le cache. Cet emplacement

est fonction du mot en mémoire. La

correspondance est la suivante numéro de

bloc modulo le nombre de blocs dans le cache

adresse

Cette structure du cache est dite à

correspondance directe.

Rappel Modulo n reste de la division par n

10

Cache à correspondance directe 8 entrées

Exemple

Mémoire Centrale

UC

11

Cache à correspondance directe 8 entrées

?

00001 00101

000 001 010 011 100 101 110 111

UC

01001 01101

10001 10101

11001 11101

Adresse

Donnée

Adresse

Donnée

12

Cache à correspondance directe 8 entrées

00001 00101

000 001 010 011 100 101 110 111

UC

1 mod 8 1

01001 01101

10001 10101

11001 11101

13

Cache à correspondance directe 8 entrées

00001 00101

000 001 010 011 100 101 110 111

UC

01001 01101

10001 10101

11001 11101

14

Cache à correspondance directe 8 entrées

00001 00101

000 001 010 011 100 101 110 111

UC

01001 01101

Aux 4 adresses 00001, 01001, 10001, 11001

correspond la même entrée dindex (adresse dans

le cache) 001 du cache

10001 10101

11001 11101

15

Cache à correspondance directe 8 entrées

000 001 010 011 100 101 110 111

UC

16

Cache à correspondance directe 8 entrées

000 001 010 011 100 101 110 111

UC

PROBLEME Un emplacement dans le cache peut

appartenir à plusieurs emplacements

mémoire. Comment savoir si la donnée correspond

au mot demandé ?

17

Cache à correspondance directe 8 entrées

Donnée

Etiquette

000 001 010 011 100 101 110 111

UC

Réponse Une Étiquette permet de savoir si

le mot demandé est dans le cache

18

Cache à correspondance directe 8 entrées

00001 00101

000 001 010 011 100 101 110 111

01

UC

01001 01101

10001 10101

00

11001 11101

Index Etiquette donnée

19

Question 1

- Où placer un bloc?

- Caches à correspondance directe

- Caches totalement associatifs

- Caches associatifs par ensemble

20

Les caches totalement associatifs

Si un bloc peut être placé nimporte où dans le

cache, celui ci est totalement associatif.

21

Les caches totalement associatifs

?

00001 00101

000 001 010 011 100 101 110 111

UC

01001 01101

10001 10101

11001 11101

22

Les caches totalement associatifs

00001 00101

000 001 010 011 100 101 110 111

UC

01001 01101

10001 10101

11001 11101

23

Question 1

- Où placer un bloc?

- Caches à correspondance directe

- Caches totalement associatifs

- Caches associatifs par ensemble

24

Caches associatif par ensemble

- Si un bloc peut être placé dans un ensemble

restreint de places dans le cache, le cache est

dit associatif par ensemble de blocs. Un ensemble

est un groupe de blocs dans le cache. - Un bloc est dabord affecté à un ensemble, puis

placé nimporte où dans lensemble. - numéro de lensemble

- numéro de bloc (adresse) modulo le nombre

densembles dans le cache

25

Cache associatif par ensemble de 2

00001 00101

Et D Et D

UC

0 1 2 3

01001 01101

10001 10101

Ensembles

11001 11101

26

Cache associatif par ensemble de 2

00001 00101

Et D Et D

UC

0 1 2 3

01001 01101

10001 10101

17 mod 4 1

11001 11101

27

Alors quel cache est à utiliser ?

- Augmenter le degré dassociativité présente

généralement lavantage de diminuer le taux de

défaut. (Voir TD) - Mais cela a tendance à augmenter le coût et le

temps daccès.

28

But du cours

- Question 1 Où placer un bloc?

- Question 2 Comment un bloc est-il trouvé ?

- Question 3 Quel bloc remplacé lors dun défaut

? - Question 4 Comment sont traités les écritures?

29

Organisation de la mémoire principale

Rappels

Adresse de loctet

Adresse du mot

0 1 2 3 4 5 6 7 8 9 10 11

0 4 8

30

Organisation de la mémoire principale

Adresse de loctet

Adresse du mot

Mémoire

0 1 2 3 4 5 6 7 8 9 10 11

0 4 8

Transfert du mot de 32 bits

Cache

4 5 6 7

Pour me déplacer dans le bloc il faut 2 bits

dadresse

31

Comment trouver un bloc ?

Réponse Quelle est la relation de ladresse UC

avec le cache ?

Cache direct

Déplacement dans le bloc

Index

Etiquette

Taille Log2(blocCache)-1

Cache associatif par ensemble de bloc

Déplacement dans le bloc

N ensemble

Etiquette

Remarque en augmentant dun facteur de deux

lassociativité on diminue de 1 bit la taille de

lindex.

32

Exemple Cache à correspondance directe

Succès

Validité Etiquette donnée

Index

0 1 2 ... ... ... ... ... ... 1022 1023

33

UC veut la donnée qui est à ladresse

UC

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Index

Adresse doctet

Etiquette

Validité Etiquette donnée

Index

0 1 2 ... ... ... ... ... ... 1022 1023

32

34

Lindex sélectionne une entrée du cache

UC

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Index

Adresse doctet

Etiquette

Validité Etiquette donnée

Index

0 1 2 ... ... ... ... ... ... 1022 1023

32

35

Compare létiquette

UC

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Index

Adresse doctet

Etiquette

Validité Etiquette donnée

Index

0 1 2 ... ... ... ... ... ... 1022 1023

36

Le mot est délivré au processeur.

UC

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Index

Adresse doctet

Etiquette

SUCCES

Validité Etiquette donnée

Index

0 1 2 ... ... ... ... ... ... 1022 1023

32

ET

37

En cas de défaut

UC

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Index

Etiquette

Donnée

Cache

Défaut/succès

Adresse

Donnée

Mémoire

Un défaut de cache génère une suspension (ou

attente), semblable aux suspension de pipeline

38

Exemple Par ensemble (256) de 4 blocs

4 Blocs

V E D

V E D

V E D

V E D

Index

0 1 2 ... ... ... ... ... ... 253 254 255

256 Ensembles

Multiplexeur 4 par 1

Succès

Donnée

39

Par ensemble (256) de 4 blocs

UC

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Adresse doctet

4 Blocs

V E D

V E D

V E D

V E D

Index

0 1 2 ... ... ... ... ... ... 253 254 255

256 Ensembles

Multiplexeur 4 par 1

Succès

Donnée

40

Par ensemble (256) de 4 blocs

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Adresse doctet

22

8

V E D

V E D

V E D

V E D

Index

0 1 2 ... ... ... ... ... ... 253 254 255

Multiplexeur 4 par 1

Succès

Donnée

41

Par ensemble (256) de 4 blocs

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Adresse doctet

22

8

V E D

V E D

V E D

V E D

Index

0 1 2 ... ... ... ... ... ... 253 254 255

Multiplexeur 4 par 1

Succès

Donnée

42

Par ensemble (256) de 4 blocs

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Adresse doctet

22

8

V E D

V E D

V E D

V E D

Index

0 1 2 ... ... ... ... ... ... 253 254 255

Multiplexeur 4 par 1

Succès

Donnée

43

Les étiquettes en fonction du type de caches

Pour des caches de même dimension

Correspondance directe

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Index

Etiquette

Associatif par ensemble de bloc

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Adresse doctet

Etiquette

Index

Totalement associatif

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Adresse doctet

Etiquette

44

But du cours

- Question 1 Où placer un bloc?

- Question 2 Comment un bloc est-il trouvé ?

- Question 3 Quel bloc remplacé lors dun défaut

? - Question 4 Comment sont traités les écritures?

45

Quel bloc remplacé lors dun défaut ?

- Il existe trois stratégies principales employées

pour choisir le bloc à remplacer - FIFO (Pas bonne)

- Le hasard (facile à réaliser)

- Le plus ancien (LRU Least Rencently Used). Ceci

utilise un corollaire de la localité temporelle.

Remarque de LRU.

46

Les défauts de caches

- Défauts obligatoires de chargement (défaut de

démarrage à froid). Un bloc accédé pour la

première fois nest pas dans le cache. - Défauts de capacité. Si le cache ne peut contenir

tous les blocs nécessaires au cours de

lexécution dun programme - Défauts de conflits (défaut de collision). Si la

stratégie de placement de bloc est associative

par ensembles de blocs ou à correspondance

directe, des défauts de conflit surviendront, car

un bloc peut être rejeté puis récupéré si trop de

blocs sont en correspondance avec le même

ensemble.

47

But du cours

- Question 1 Où placer un bloc?

- Question 2 Comment un bloc est-il trouvé ?

- Question 3 Quel bloc remplacé lors dun défaut

? - Question 4 Comment sont traités les écritures?

48

Comment sont traités les écritures?

- Lécriture simultanée (ou rangement simultané)

- Linformation est écrite à la fois dans le bloc

du cache et dans le bloc de la mémoire de niveau

inférieur. - La réécriture (la recopie)

- Linformation est écrite uniquement dans le bloc

du cache. Le bloc modifié du cache est recopié en

mémoire principale uniquement quand il est

remplacé.

49

Comment tirer parti de la localité spatiale ?

- Le cache que nous avons décrit jusquà présent ne

tire pas parti de la localité spatiale dans les

requêtes. En effet, chaque mot dispose de son

propre bloc. - EXEMPLE

- Supposons que les adresses doctets suivantes

soient demandées par un programme

50

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

UC

01001 01101

10001 10101

11001 11101

51

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

UC 16

01001 01101

10001 10101

16 10000

Etiquette Index

11001 11101

52

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

UC 16

01001 01101

DEFAUT

10001 10101

16 10000

Etiquette Index

11001 11101

53

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

10

UC 16

01001 01101

10001 10101

16 10000

Etiquette Index

11001 11101

54

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

UC 19

01001 01101

10001 10101

19 10011

Etiquette Index

11001 11101

55

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

UC 19

01001 01101

DEFAUT

10001 10101

19 10011

Etiquette Index

11001 11101

56

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

UC 19

01001 01101

10

10001 10101

19 10011

Etiquette Index

11001 11101

57

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

UC 17

DEFAUT

01001 01101

10

10001 10101

17 10001

Etiquette Index

11001 11101

58

Exemple 16,...,19,...,17

000 001 010 011 100 101 110 111

Bilan 3 défauts

UC

10

59

Comment diminuer les défauts

Ce Dupont .... Dans mes bras

Augmenter la taille des blocs

THE BOSS

60

Caches à 4 mots mémoire

00001 00101

000 001 010 011 100 101 110 111

UC

01001 01101

10001 10101

11001 11101

61

Caches à 4 mots mémoire

00001 00101

000 001 010 011 100 101 110 111

UC

01001 01101

10001 10101

11001 11101

2 bits

3 bits

index

adresse dans le bloc

remarque pas détiquette

62

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

UC

01001 01101

DEFAUT

16

10001 10101

11001 11101

100 00

index

adresse dans le bloc

remarque pas détiquette

63

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

UC

01001 01101

16 17 18 19

16

10001 10101

On ramène les ref 16,17,18,19

16 10000

11001 11101

index

adresse dans le bloc

remarque pas détiquette

64

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

succès

UC

01001 01101

16 17 18 19

19

10001 10101

19 10011

11001 11101

index

adresse dans le bloc

remarque pas détiquette

65

Exemple 16,...,19,...,17

00001 00101

000 001 010 011 100 101 110 111

succès

UC

01001 01101

16 17 18 19

17

10001 10101

17 10001

11001 11101

index

adresse dans le bloc

remarque pas détiquette

66

Exemple 16,...,19,...,17

- Bilan 1 seul défaut survient pour trois

références. - SUPER JE SUIS LE MEILLEUR

67

Exemple de réalisation

31 30 29 28 ...............16 15 14 13 12 11 10 9

...4 3 2 1 0

Index

Adresse doctet

Etiquette

Validité Etiqu donnée 128 bits

Adresse dans le bloc

Index

0 1 2 ... ... ... ... ... ... 254 255

32

Mux

68

Exemple 16,...,19,...,17

- Bilan 1 seul défaut survient pour trois

références. - SUPER JE SUIS LE MEILLEUR

DUPONT and Co

69

Si nous avons les temps daccès suivants

- 1 cycle dhorloge pour envoyer ladresse

- 10 cycles dhorloge pour chaque accès mémoire

- 1 cycle dhorloge pour envoyer un mot de donnée.

- Total 3 (1101) 36 cycles

70

Exemple 16,...,19,...,17

- Reprenons les chiffres précédent

- 1 cycle dhorloge pour envoyer ladresse

- 10 cycles dhorloge pour chaque accès mémoire

- 1 cycle dhorloge pour envoyer un mot de donnée.

- Total 141041 45 cycles

- Le gain nest pas ici énorme !!!!!.

- Comment diminuer ce temps ?

71

Tirer parti de la localité spatiale

- Question De quelle manière une plus grande

taille de bloc influence-t-elle les performances

? - Le taux de défauts chute lorsque nous augmentons

la taille de bloc. - Attention il faut adapter le système mémoire en

conséquence.

72

UC

UC

Cache

Cache

Bus

Bus

B M

B M

B M

B M

Mémoire

73

Organisation dune mémoire entrelacée

Adresse externe a4b

b b b b

0 1 2 3 4 5 6 7 8 9 . . .

Mémoire entrelacée

Mot 1 Mot 2 Mot 3 Mot 4

74

Encore plus compliqué

- ATTENTION (voir TD)

- Le taux de défaut peut augmenter, si la taille de

bloc est prise très grande par rapport à la

taille du cache, car le nombre de blocs pouvant

être contenus dans le cache deviendra petit, et

la compétition entre ces blocs sera rude. Par

conséquent un bloc sera éjecté du cache avant

quun grand nombre de ses mots soit accédé. - Le coût du défaut croît. Car le temps

nécessaire(si on ne modifie pas le système

mémoire).

75

Les performances des caches

- Le temps UC est divisé entre les cycles dhorloge

passés par lUC à exécuter le programme et les

cycles dhorloge que lUC passe à attendre le

système mémoire.

Tps UC (Cycles dexécution UC Cycles

dattente mémoire) Tps C

76

Les cycles dattente mémoire

- Les cycles dhorloge dattente mémoire

proviennent principalement des défauts de cache. - (Une prédiction précise des performances implique

généralement des simulations très détaillées du

processeur et du système mémoire).

Cycles dattente (Nb. dinst/programmes) mémoir

e (Nb. de défauts/instruction) Coût

défaut

Cycles dattente (Nb. d'accès par

programme) mémoire (taux de

défaut) Coût défaut

77

Résumé

- Où peut être placer un bloc ?

- Un corresp. direct, plusieurs (associatif par

ensembles), ou tout (totalement associatif)

endroit. - Comment un bloc est il trouvé ?

- Indexation (correspondance direct)

- Recherche limitée (associatif par ensembles)

- Recherche totale (totalement associatif)

- Quel bloc est remplacé lors dun défaut ?

- Généralement, soit le moins récemment utilisé,

soit un bloc au hasard, de manière aléatoire. - Comment sont traitées les écritures ?

- Chaque niveau de la hiérarchie peut utiliser soit

lécriture simultanée soit la réécriture.

78

Résumé

- Le défi lancé par la conception des hiérarchies

de mémoires est que tout changement qui peut

améliorer le taux de défauts peut aussi affecter

de façon négative les performances globales. - Cest une combinaison d'effets positifs et

négatifs pour chaque paramètre de conception qui

rend délicate la conception dune hiérarchie de

mémoires

Changement de Conception Augmenter la

taille Augmenter lassociativité Augmenter la

taille de bloc

Effet sur le taux de défauts Réduit les défauts

de capacité Réduit le taux de défaut dû aux

défauts de conflit Réduit le taux de défaut

pour un large éventail de tailles de bloc

Effet négatif possible sur les performances Peut

augmenter le Tps daccès Peut augmenter le temps

daccès Peut augmenter le coût de défaut

79

Caches taille des blocs

Coût de léchec

Taux déchec

Tps transfert

Tps daccès

Taille du bloc

Taille du bloc

T ps daccès

Augmenter la taille du cache indéfiniment

Taille du bloc

80

(No Transcript)