PLL Jitter - PowerPoint PPT Presentation

1 / 9

Title:

PLL Jitter

Description:

... Independent DLL and PLL Based on Self-Biased Techniques' ... Experimental Setup. 9. Measurements. Part of the jitter is 'masked' in noisy jitter estimate. ... – PowerPoint PPT presentation

Number of Views:508

Avg rating:3.0/5.0

Title: PLL Jitter

1

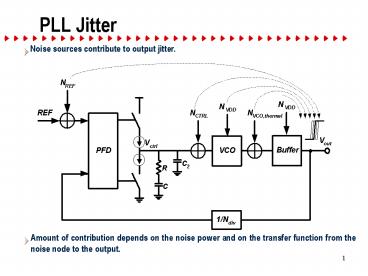

PLL Jitter

2

PLL Jitter Optimization

Adjusting the loop characteristics (wN, z)

modulates the output jitter. There exists a

minimum that depends on the noise source

characteristics.

We would like to operate at the minimum jitter

point at all times!

3

PLL Jitter Optimization

Therefore, adaptive jitter optimization is

desirable ! We are primarily interested in

relative jitter values at various PLL operating

points!

4

PLL Circuit

J. G. Maneatis, Low-Jitter Process-Independent

DLL and PLL Based on Self-Biased Techniques,

IEEE Journal of Solid-State Circuits, vol. 31,

pp. 1723-1732, Nov. 1996.

5

On-Chip Jitter Estimation

Signals track jitter boundaries

6

Dead-Zone Generation

Tracking of jitter distribution edges by the VCDL

outputs.

7

Simulation Results

Different process corners

Different operating frequencies

Changes in operating frequency and process

variations affect the position of the optimum

operating point.

8

Implementation

Die Photo

Experimental Setup

9

Measurements

- Part of the jitter is masked in noisy jitter

estimate. - CDAC, RDAC range not enough to cause jitter

increase due to phase margin degradation.