The typical Computer System Organization - PowerPoint PPT Presentation

1 / 23

Title:

The typical Computer System Organization

Description:

The CPU internal Bus represents the universal communication path within the CPU. ... ALU : The Arithmetic Logical Unit ( The Integer Processing Unit) ... – PowerPoint PPT presentation

Number of Views:86

Avg rating:3.0/5.0

Title: The typical Computer System Organization

1

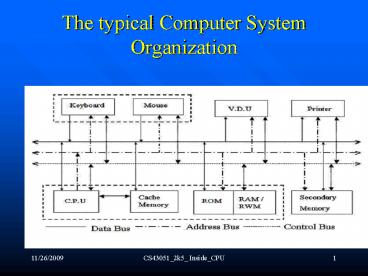

The typical Computer System Organization

2

The CPU-Devices Connectivity

- Address Bus - Group of lines that is used to

carry address information from the CPU to the

concerned device(s). Address Bus is one that

helps the CPU to select one among many devices.

Hence it is unidirectional. - Data Bus - The group of lines used to carry

data/information from the device to CPU vice

versa. It is always bi-directional. - Control Bus The group of lines that enables the

CPU to control various activities of the

concerned device e.g. Read Signal, Write Signal,

Status Set Signal. As illustrated each bus

consists of a number of lines, which is

represented in a compact manner.

Bi Directional Bus composed of 32 Lines

32

3

The Typical CPU Device Interface

From / To CPU

Address Bus

A 32

Data Bus

D 64

Control Bus

C 12

Command Register (Write Only)

Device Controller

Status Register (Read Only)

Actual Device

Buffer(s Read / Write

4

The Salient Features

- Each Bus represents a mere group of electrical

signal lines. - None of the three buses has got any storage

and/or processing capability. - The individual bus widths ( A , D C ) are NOT

related to each other in any way. - The address Bus lines are marked as a31 a0

while data bus lines are marked as d63.. d0 with

a0 , d0 representing least significant bits (LSB)

of address data respectively. - Not all the lines belonging to any bus are

connected to any device interface/ memory modules.

5

The Internal Structure of a CPU

- Inside the CPU both Address as well as Data are

manipulated during Instruction Execution. - In any computer system, the flow of Address and

Data takes place from one component to the other

component via the relevant Bus as guided by the

then executed instructions which generates the

requisite control signals carried via the

Control Bus. - This Data flow path as well as all the associated

components are termed as the Data Path. - The control signals originate from the control

unit as guided by the currently executed

instruction and carried to various points through

the internal OR the external control bus. All

this constitutes the Control Path .

6

The Key CPU components.

- Data Path Components The major portion of any

CPU . It constitutes the external Address Data

Bus as well as the internal Data / Address

storage and processing components. - Control Path Components Constitutes of the

Control Unit as well as its Input (The

Instruction Store inside the CPU) and the output

which includes both the internal as well as the

external Control Bus.

7

The CPU Activities

- 1. Data Transfer activity This involves the

following tasks - a) Writing to an External Device

Interface/Memory. - b) Reading from an External Device Interface

or Memory. - 2. Data Processing Involves both arithmetic as

well as Logical Processing. - Both of these involve Data Path Components.

- 3. Control and Sequencing Involves Control Path

Components.

8

CPU Storing Data to a Memory Location/ Sending

Data / Command to Device Interface Register(s)

Key Facts

- a) CPU knows where to write i.e. to which

address to write. There has to be some component

within the CPU that holds this destination

address . Electronic Component to hold any

address Address Register. Since mostly the

external activity deals with memory hence this

can be termed as a Memory Address Register (MAR). - b) CPU also knows what ( the data) is to be

written/stored in the specified address . There

has to be some component within the CPU that

holds the data . Electronic Component to hold any

data Data Register. Since mostly the external

activity deals with memory hence this can be

termed as a Memory Data Register (MDR) / Memory

Buffer Register (MBR). - c) The control signal Memory Write/ Device

Write (WR) is emanating from the CONTROL UNIT

within the CPU.

9

CPU Storing Data to a Memory Location/ Sending

Data / Command to Device Interface Register(s)

Key Steps

- Address Source Some CPU Register ( To be

Elaborated Later) ? MAR. - Data / Command From Some Other CPU Register (

To be Elaborated Later) ? MBR/MDR. - MAR ? Address Bus. This selects the Memory

Location/ Device Interface Buffer location where

WRITE is to take place. - MBR/MDR ? Data Bus .Write Signal from CONTROL

UNIT ? Control bus at the same time. - CPU CONTROL UNIT monitors the Control bus for

the Acknowledgement signal from the slow memory

/ device.

10

CPU Reading Data / Fetching Instruction /

Reading Status from a Memory Location/ Device

Interface Register(s) Key Facts

- a) CPU knows where to Read from i.e. from

which address to Read. There has to be some

component within the CPU that holds this d source

address . Electronic Component to hold any

address Address Register. The Memory Address

Register (MAR) is again employed for this

purpose. - b) Once obtained , CPU has to store the read

in data in some place inside it for future use

. The Memory Data Register (MDR) / Memory Buffer

Register (MBR) serves this purpose. - c) The control signal Memory / I/O Read

is emanating from the CONTROL UNIT within the CPU.

11

READ / FETCH Sequence CPU Loading Data from

Memory / Device Interface Registers OR Fetching

Instruction from Memory

- 1. Address Source Some CPU Register ( To be

Elaborated Later) ? MAR. - 2. MAR ? Address Bus.

- 3. CONTROL UNIT asserts the Read Signal

through its control bus at the same time. - 4. CONTROL UNIT next monitors the control bus

for the READY signal from the concerned slow

Memory Location/ Device interface buffer - 5. After obtaining the READY signal

- MBR / MDR ? Data Bus . The Data /

Instruction/ Status comes into the CPU . - 6. Relevant CPU Register ( To be Elaborated

Later) - ? MBR/MDR.

12

CPU / External World Interface

CPU Internal DATA /ADDR BUS

Within CPU

Outside CPU

MAR ( 32 bit)

Address Bus

MBR / MDR ( 64 bit)

Data Bus

CONTROL Unit

Control Bus

13

Other CPU Components - 1

- The CPU internal Bus represents the universal

communication path within the CPU . It carries

address , data as well as instruction. For any n

bit CPU its internal bus will be n bit wide

normally. Here n 32. But external Data Bus

width can be different (64 bit wide) here. Here

we have assumed an Uni-Bus structure for

convenience. However there exists CPU with 2-Bus

(IN Bus / OUT Bus) or 3 BUS (IN 1 Bus, IN 2

Bus OUT Bus) structure. - There must be other CPU registers feeding to /

taking from this bus. - General Purpose Registers (GPRs) , a group of

Registers with two port accessibility can be used

to generate / store both address as well as

data.

14

Other CPU Components 2The Instruction Fetch

Store

- The CPU must be able to distinguish an

instruction from a data . This it achieves from

the very starting point of a Read Operation by

noting the source of this address generation. The

Instruction address is generated from a special

register termed as the Instruction Pointer (IPTr)

/ Program Counter (PC). - The Instruction once obtained in the MBR/MDR is

stored in another special register termed as the

Instruction Register (IR).

15

The Processing Unit

- All data processing is carried out by purely

combinational blocks. However in modern day CPUs

following types of operations take place - 1a) Integer Arithmetic.

- 1b) Logical Operations involving Integers.

- 2a) Floating Point Arithmetic.

- 2b) Logical Operations involving floating

point Numbers. - However there exists a separate Floating Point

Unit (FPU) in modern day CPUs to handle all

floating point operations ( Not to be Considered

Now). - So we assume that our CPU only handles Integers

using ALU ( The Arithmetic Logic Unit ) which is

a purely combinational block i.e. cannot Store

anything.

16

The Integer ALU and its associated Components

- Most operations are Binary in Nature hence

require two operands. - In order to ensure proper processing , both the

operands should be kept steady for sometime at

the ALU Inputs.( Data Setup time). Hence normally

there has to be two(2) Operand Registers feeding

to the ALU Inputs. - Similarly , the Result Produced by the ALU should

also be stored in a Register/Buffer. - All of the aforesaid Registers, wherever present,

are exclusively meant for ALU usage hence remain

inaccessible to the users/programmers. - The ALU can perform various functions out of

which the function relevant to the Instruction

being executed is to be selected by the Control

Unit.

17

The Typical Organization of an n Bit ALU

From CPU Internal Uni-Bus

n Bits

n Bits

WRCLK B En

WRCLK B En

Opnd 1 Register A (n bit PIPO)

Opnd 2 Register B (n bit PIPO)

WRCLK A En

From CPU Int. BUS

n Bits

n Bits

ALU Control Signal Generator

n bit Combinational Unit

ALU Op-Code/ ALU Function Control

k Bits

(m-k) Bits

4

Group MUX

MUX Control

C_in

MUX Control

FlagWRCLK En

Output Enable

Flag Reg.S m no. F/Fs

Result Register C ( n bit PIPO)

WRCLK C En

n Bits

m Bits

Flag WR Clock En

From Instruct. Register

Common Output Enable To CPU Internal BUS

18

The typical ALU Operation Sequence

- Operand A Register ? One Source Operand Some

CPU Register Content (usually a GPR) via

Uni-Bus). - Operand B Register ? The Other Source Operand

From Some CPU Register Content (usually a GPR)

(via Uni-Bus). Select ALU Function. - Write Result into Result Register as well as

Write Flag F/Fs. - Designated Destination Some CPU Register

(usually a GPR) ? Result Register content (via

Uni-Bus).

19

Structure of Data Path (Internal to the

CPU)(Minimum Configuration )

Main Memory RW M

Bidirectional Tri State Buffer / Register

External Address Bus

Ext. Data Bus

MDR / MBR

MAR

CPU Internal Bus

IR

Iptr / PC

SP

Op1

Op2

CONTROL BUS

GPR File

Control Unit

One ALU

Result

Flag

20

CPU Data Path Components , Summarized

Description - 1

- IR -gt Instruction Register used to store the

current instruction fetched/read/retrieved from

Main Memory. - Stack Pointer (SP) -gt Helps to maintain a

Hardware LIFO memory (usually from Higher to

Lower Address). - IPTr/ PC-gt Instruction Pointer/ Program Counter

contains the address of the next instruction in

Main Memory to be executed. Preserved in Stack

automatically by the Control Unit before

executing any CALL/ Software Interrupt or

Servicing any Interrupt. - MAR -gt Memory Address Register acts as the

gateway between the CPU and the address bus /

MMU(not shown). - MDR /MBR-gt Memory Data / Buffer Register acts as

the gateway between the CPU and the data bus.

21

CPU Data Path Components , Summarized

Description - 2

- GPR File The Group of General Purpose Registers

acting as scratch pad of the CPU. Used by the

ALU for Input Operands as well as storing

computed Result. These are also employed as

address pointers. All the GPRs happen to be

programmer accessible as well as accessible to

all processes. - Control Unit The Control Unit implements the

instruction set of the CPU . This contains the so

called firmware ( control Informations for all

types of register transfer processing

operations) .It controls and sequences all

activities associated with the computer.

22

CPU Data Path Components , Summarized

Description - 3

- ALU The Arithmetic Logical Unit ( The Integer

Processing Unit). It being a purely combinational

unit , it must be fed by two Operand Registers as

well as Result obtained in Result Register. All

of these registers are programmer inaccessible. - PSW - gt The Program Status Word , consists of the

last computed result / Result Register

condition code flags like ZERO (for Zero Result)

, Sign (for ve result) Carry etc as a whole. To

be preserved in Stack before any Call / servicing

any Interrupt.

23

The Instruction Set Architecture ( ISA) Design

Issues

- The Data Path Components and their connectivity.

- The Assembly Instruction Set of the underlying

CPU (as implemented by its Control Unit the

Firmware ). - The role of the various Internal Data Path

Components in Instruction Execution. - Specifying the Data Transfer Protocols between

CPU and associated peripherals in terms of the

existing instruction set and all the associated

data path components. - Design outline of the Control Unit.