Cordic PowerPoint PPT Presentations

All Time

Recommended

... (shifting by 1 or 7 takes same time) Sign extension. Shifter dataflow schematic ... A survey of CORDIC algorithms for FPGA based Computers. [2] Behrooz Parhami. ...

| free to view

Performs vector rotations of arbitrary angles using only shifts and adds. ... purpose CORDIC processor for the price of a specialized one. Switch between modes ...

| free to download

Data length of estimation of carrier freq. offset. 16. Can be up to 48. Critical path delay. 12.7 ns. 50 ns for 802.11a. Silicon area. 397080 um2. Total power ...

| free to view

Fast Compilation for Reconfigurable Hardware ... Cordic Honeywell timing benchmark for vector rotation. ... IDEA PGP encryption algorithm.

| free to download

numerical and structural properties. Arithmetic Level. e.g., MAC/DIV/SQRT or CORDIC ... Post-layout measurements. Verification. Design Example. Applications ...

| free to view

LOW POWER RECONFIGURABLE CORE. FOR 3D GRAPHICS SHADING AND TEXTURE ... Interpol. (Gouraud) Normal. Interpol. Cordic (Phong) 32. 32. 8. 8. Reconfig. Data. G_Clk1 ...

| free to view

CORDIC ALGORITHM WITH DIGITS SKIPPING. Javier Hormigo, Julio Villalba and Emilio L. Zapata ... After n/3 iterations, only the angles aj fulfilling dj=1 are ...

| free to view

1.E. Doukhnitch, 'Synthesis for the Discrete Quaternion Transform Algorithms Class', in Proc. ... of a 4-D quaternion processor. HOUSEHOLDER TRANSFORMATION ...

| free to view

100 02 01 101 7 31 ...

| free to download

Implementation of a noise subtraction algorithm using Verilog HDL University of Massachusetts, Amherst Department of Electrical & Computer Engineering, Course 559/659

| free to view

Are you on the lookout for DSP project ideas? you have landed in the right place. In this article, Takeoff Edu Group will talk about some interesting DSP Project Ideas and students of the engineering fraternity can work upon these as a Final Year Project. Our project ideas for DSP Student and Engineers will help you Get Inspired. DSP is a complex of modern technologies, which have become an important part not only of telecommunications but also for the audio and video processing, control systems, etc. If you are a student or an engineer seeking a DSP project to do, this is the page you should read. Our collection of DSP project ideas may be used to gain practical knowledge and skills demonstration.

| free to download

Title: Sin t tulo de diapositiva Author: Alex Last modified by: gpaa Created Date: 9/16/1999 9:25:38 PM Document presentation format: Presentaci n en pantalla

| free to view

Logarithms Method 1 (Example) -ln x = (1.-1) ln(1.01) ln(1.0000-1) 1. 0 0 0 0 0 1 ... Logarithms Method 2 (Example) (x2/2)2/2 = 1.00101100001. y3 = 0 ...

| free to download

A Systematic Design Approach to Implement Interference ... Bruno Haller (Lucent Technologies) Bob Brodersen. January 2000. Problem Statement. Applications ...

| free to view

Focussing subsystem. Electronic vs. Mechanical. Sharper images are produced ... How is this focussing achieved digitally? Beamforming Fundamentals ...

| free to view

Feature extraction, Quantisation/Distance Calculation. Recognition ... curvature calculation, Hough transform. Comparison-based operations ...

| free to view

Can exploit shared twiddle factor properties (i.e. sub-expression sharing) to ... two properties in the twiddle factors: Symmetry Property: Periodicity Property: ...

| free to view

Primary design criterion is power minimization. Existing Solutions ... Six 31-tap, pilot match FIR filters account for 70% of total design area ...

| free to view

Digital Phase Control System for SSRF LINAC C.X. Yin, D.K. Liu, L.Y. Yu SINAP, China Email: yincx@sinap.ac.cn

| free to view

Hitachi SH-4. 16-BIT FIXED POINT (95% of market): TI TMS320C2X, TMS320C62xx ... Hitachi SH3-DSP. StarCore SC110, SC140. Data path configured for DSP ...

| free to view

... IIR filter Serial line monitor ... Complete termios support Complete set of IOC shell commands Memory pool free space available as PV spy command Hooks ...

| free to download

Module Design Tradeoffs. Custom Design. Fewer & More Rigid Leaf Cells (specific purpose) ... Designs. Performance & Area Sacrificed. Custom vs. General Design ...

| free to view

Title: Benchmarking Tools and Assessment Environment for Configurable Computing Author: HTC/IS KeyServer Last modified by: Richard B. Katz Created Date

| free to view

... http://rateyourmusic.com/list/boima1/top_30_rappers_of_all_time_f1/2/ , http://rateyourmusic.com/list/boima1/top_30_rappers_of_all_time_f1 . Pripravil/a: ...

| free to view

Floor-plan information -15 - Critical Path Delay Estimation. Use block-level linear timing model. Use block connectivity and floor-plan information to determine ...

| free to view

A BPSK / QPSK Timing Error Detector for Sampled Receivers. ... Oscilloscope. Personal Computer. Xilinx ISE. ModelSim Simulator. MATLAB. Modulator Board ...

| free to view

Ambient Diffusion Specular. I (R,G,B) = Pixel Lighting Value ... Ambient, Diffused, Specular (Phong) Gouraud. RECONFIGURABLE. SHADING CORE. Algorithm ...

| free to view

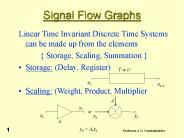

Signal Flow Graphs A Linear Time Invariant Discrete Time Systems can be made up from the elements { Storage, Scaling, Summation } Storage: (Delay, Register)

| free to download

FPGA Co-Processor Enhanced Ant Colony Systems Data Mining Jason Isaacs and Simon Y. Foo Machine Intelligence Laboratory FAMU-FSU College of Engineering

| free to download

Software Version v2.2 Electronic Product Design Design Flow Time-to-Market Raising the abstraction level Code compactness Algorithmic description FIR filter 100 lines ...

| free to view

Attenuation. Sharing. Modulation. Multiply carrier(s) BFSK, BPSK, QPSK, OFDM, Spread spectrum ... Poles can boost frequencies, zeroes can only attenuate them ...

| free to download

Matrix formulation for 1D and 2D signals. Discrete Fourier Transform (DFT) ... Discrete Cosine/Sine Transform. DCT: Fast DCT. see note: fastdct.doc. 2D DCT. DST ...

| free to view

C2670 cc dalu i9 tcon. C3540 cht decod k2 term1. C432 cm138a des lal too_large ... BDD may be more efficient than SOP form. Data hardcoded into program ...

| free to view

Computing Faster without CPUs Scientific Applications on FPGA-based* Reconfigurable Hypercomputers by Dr. Olaf Storaasli Analytical & Computational Methods Branch

| free to download

Design a 1.6 Mbps DSSS timing recovery unit. Modulation. Length 31 PN code ... Core VDD = 1V, Pad VDD = 1.8V, on-chip level shifters for conversion. Status and Results ...

| free to view

laboratoires elmi & a2si esiee paris soutenance de projet conception de formes 3d avec un laser r mi bin mathieu stephan lise talbotier plan page 2/25 le materiel l ...

| free to download

Netlist and Floor Plan of. Macro Modules Standard Cells. Back-end Design flow ... with PDA Models. Data Flow (construct with parameterized modules) ...

| free to view

How to create beam-forming smart antennas using FPGAS If you could squeeze two or three times more cellular telephone conversations into the same amount of bandwidth ...

| free to download

Department of Computer Science & Engineering. Indian Institute of Technology Delhi ... The resource section lists the definitions of all objects which are required to ...

| free to view

Low power logic styles. Reconfigurable blocks. Low power data path components ... Classic problems well defined. Advancements will have a huge impact ...

| free to download

A|RT Designer V2.2 - Training - page 1. Training. Software Version v2.2 ... intelligent - it checks whether the code is C/C compliant, if there are non ...

| free to view

Output to a Accumulator to Simulate Rotating Phasor. Rotator. Rotates Chosen Stream by Sum of DPLL Phase Update and Accumulator Phase Update. Correlator ...

| free to view

System Architecture Template. Concepts of Reconfigurable Interconnect ... Dynamic configuration context switch using multiple-context configuration memories. ...

| free to view

Engineering Applications on NASA s FPGA*-based Hypercomputers By Olaf.O.Storaasli@nasa.gov Analytical & Computational Methods Branch NASA Langley Research Center

| free to download

Duality. NAND gates network. NOR gates network. Duality provides flexibility for low level implementation. NAND gates are good for static CMOS. ...

| free to download

WIRELESS COMMUNICATIONS From Systems to Silicon Raghu Rao Wireless Systems Group, Xilinx Inc. Agenda Introduction to Wireless communications Systems design and ...

| free to download

The theory of bi-decomposition was developed by Bernd Steinbach and his ... B.Steinbach, F.Schumann, M.Stockert. Functional Decomposition of Speed Optimized Circuits. ...

| free to view

Small wavelength allows for multi-antenna approach in reasonable form factors. 57 dBm ... 60 GHz Channel Spatial Properties. Specular, moderately reflective channel ...

| free to view

... Algorithms and Hardware Design. Instructor: Prof. Chung ... Why do we care about arithmetic algorithms and hardware design? Classic problems well defined ...

| free to download

10Base-T Ethernet with RJ45 jack. Compact Flash slot for expandability. Linux Kernel 2.4 as OS ... Black. Box. Controller. VHDL. StateFlow. Control Signals ...

| free to view

ELEC692 VLSI Signal Processing Architecture Lecture 8 ... Utilization of multipliers increased to 75% due to storage of 3 out of radix-4 butterfly outputs.

| free to view

Ternary shifting. Comparison between barrel shifter and log shifter. 10 ... Extend the fanout splitting idea and ILP formulation to ternary shifter ...

| free to download

... of IP through custom executables. Maintain executables on-line as Java applets ... executables from server. app2.class. Applet executes within. user's browser ...

| free to view

Fab-less design houses turn innovative design into profitable chip sets using CAD tools. ... For a particular implementation option, how to achieve optimal design? ...

| free to view