Embedded Systems: Hardware - PowerPoint PPT Presentation

Title:

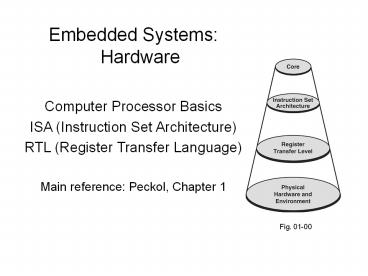

Embedded Systems: Hardware

Description:

Embedded Systems: Hardware Computer Processor Basics ISA (Instruction Set Architecture) RTL (Register Transfer Language) Main reference: Peckol, Chapter 1 – PowerPoint PPT presentation

Number of Views:201

Avg rating:3.0/5.0

Title: Embedded Systems: Hardware

1

- Embedded Systems Hardware

- Computer Processor Basics

- ISA (Instruction Set Architecture)

- RTL (Register Transfer Language)

- Main reference Peckol, Chapter 1

Fig. 01-00

2

fig_01_01

Basic components

Common bus structure address, data, control

fig_01_01

fig_01_03

3

fig_01_05

Some processor options (note firmware)

1. Microprocessor-based system

fig_01_05

2. Microcontroller-based system Fig. 1-05

components integrated into one unit)

fig_01_07

DSP (A/D, D/A high speedvideo, audio, images

fig_01_06

4

fig_01_08

DATA DATA TYPES

NUMERIC --Unsigned integer --Signed integer (2s

complement, sign-magnitude, fixed point,

etc.) --Floating point 3 components sign expon

ent mantissa

fig_01_08

NONNUMERIC --address --character

5

fig_01_09

- Numeric data

- Range is always limited. Number of digits of

resolution is size of fractional part. - Example in 4 numeric bits

- Number of bits in fraction range

- 0 (integer) 0-15

- 1 xxx.x 0-7.5

- (fractions 0, ½)

- 2 xx.xx 0-3.75

- (fractions, 0, ¼, ½, ¾)

- 3 x.xxx 0-1.875

- (fractions, 0, 1/8, ¼, 3/8, ½, 5/8, ¾, 7/8)

6

fig_01_09

Most base 10 fractions cannot be represented

exactly in binary Example how to represent 2.x

in 4 bits, with 2 bits of resolution? Choices

2.0, 2.25, 2.5, 2.75, 3.0 2.1 ? 2.0 or 2.25 2.2 ?

2.0 or 2.25 2.3 ? 2.0 or 2.25 or 2.5

fig_01_09

r

rounding

truncation

truncation

Error range for n bits of resolution Truncation

-2-n lt Etruncation lt 0 Rounding - ½ 2-n lt

Erounding lt ½ 2-n Computation which is easier

to compute?

rounding down

rounding up

7

fig_01_09

Error propagation in arithmetic Examples Conside

r two numbers whose true values are N1 and N2 and

whose values in the computing system are N1E and

N2E Addition errors add N1E N1 E1 N2E

N2 E2 N1E N2E (N1 E1) (N2

E2) N1 N2 E1

E2 Multiplication error N1E N2E (N1

E1) (N1 E2) (N1N2) (N2 E1 N1

E2) (E1 E2) term 1 term

2 Note that if term 2 is neglected then error

depends on size of N1 and N2

8

fig_01_10

Another example (pp. 11-12 of text) measuring

power dissipated in resistor R in the following

circuit Suppose E 100 VDC /- 1, I 10A

/- 1, R 10 ohms /- 1. 3 methods of

caluculatin power dissipated, neglecting lower

order error terms a. E1 (100V /- 1) (10A

/- 1) 998.9 ? 1001.1 b. I2R (10A /- 1)

(10A /- 1) (10 ohms /- 1) 997 ? 1003 c.

E3 (100 V /- 1)(100 V /- 1) / (10 ohms /-

1) 908.9 ? 1111.3 Which should we

use? optimistic a middle-of-the-road

average of a,b,c safest c

fig_01_10

9

- InstructionsISA level

- Instruction coding

- HLL (high level language, C, C , e.g.)

- assembly language (ISA)

- machine language

- (can work at any level high level allows faster

but less efficient coding) - IEEE Standard 694-1985IEEE standard for

microprocessor assembly languageused for

examples in text

10

operator addr mode operand(s)

Instruction coding Fields operator, operands

(type of addressing) Example 32 bits 3 bits

opcode 2 bits address mode (e.g. direct,

indirect, indexed, immediate) 27 bits for

addressing operand (s) Expanding opcode

(example) 000-110xxxxxxx 2 operands 1110xxxx

xx 1 operand 1111xxxxxx no operand (e.g.,

HALT)

11

fig_01_13

Example instruction formats

fig_01_14

fig_01_13

fig_01_15

12

Instructions Instruction types arithmetic /

logical data movement control Arithmetic /

logical instructions operator number of

operands arity (unary, binary, three-operand,

) Examples x -x negation, assignment x

y assignment x x y addition,

assignment z x y addition, assignment

13

fig_01_42

Typical ALU and registers

fig_01_42

14

fig_01_43

Common ALU functions

fig_01_43

Cannot be affected by interrupt

15

fig_01_44

Common ALU functions (continued)

fig_01_44

16

fig_01_45

Common ALU functions (continued) Question

what is a minimal set of ALU instructions?

fig_01_45

17

fig_01_16

Data movement instructions source / destination

fig_01_16

18

fig_01_17

Common data movement instructions

fig_01_17

Question how can you implement XCH without

using a temporary variable?

19

fig_01_12

Addressing modes Immediate MOVE A,

BH Direct MOVE OPR1, OPR2 Indirect MOVE

OPR1, myVarPtr MOVE OPR1, OPR1 MOVE

OPR1, yPtr Register direct MOVE Reg1,

Reg2 Register indirect MOVE Reg1,

Reg2 Indexed (loops) MOVE Reg1, OPR2REG2 PC

relative (loops,e.g. offset can be

negative) ADD PC, Reg1 Example what is

the difference between Y, Y, Y

fig_01_12

Indirect addressingmyVarPtr holds address or

myVar

20

fig_01_21

Addressing examples

fig_01_21

21

fig_01_22

fig_01_22

22

fig_01_23

fig_01_23

23

fig_01_24

fig_01_24

24

fig_01_25

Control instructions Control can be sequential

(default) loop (pre or posttest) branch go

to conditional (if, if-else,, case, branch on

condition) procedure or function calll

25

fig_01_29

Branch instructions Typical condition

codes Typical branch instructions

fig_01_29

fig_01_30

26

fig_01_31

Example of conditional statements C / assembly

language

fig_01_31

fig_01_32

27

fig_01_34

Looping example

fig_01_34

fig_01_35

28

fig_01_36

Function or procedure call Must store return

address, pass information back and

forth What are standard parameter

passing methods?

fig_01_36

fig_01_37

29

fig_01_39

Stack common way to handle procedure / function

calls Q what are two alternative methods

for handling function / procedure calls? Which

methods facilitate recursion?

fig_01_39

30

fig_01_40

Function call example

fig_01_40

fig_01_41

31

Question can you design a general-purpose

computer with a 3-bit opcode?

32

fig_01_46

Different viewpoint RTL register-transfer

language level

fig_01_46

33

fig_01_49

Register behavior Read / Write Serial / Parallel

fig_01_49

fig_01_51

fig_01_50

34

fig_01_52

RTL VIEW

fig_01_52

fig_01_53

35

fig_01_54

Instruction execution cycle Q Where is

this step implemented?

fig_01_55

fig_01_54

36

fig_01_57

Multiple levels--examples

fig_01_57

37

fig_01_58

fig_01_58

38

fig_01_59

fig_01_59

39

table_01_03

table_01_03