Bus Architecture - PowerPoint PPT Presentation

Title:

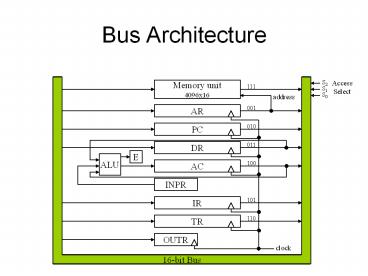

Bus Architecture

Description:

Bus Architecture S2 Access Select Memory unit 4096x16 111 S1 S0 address 001 AR 010 PC 011 DR E ALU 100 AC INPR 101 IR 110 TR OUTR clock 16-bit Bus – PowerPoint PPT presentation

Number of Views:1197

Avg rating:3.0/5.0

Title: Bus Architecture

1

Bus Architecture

S2

Access Select

Memory unit 4096x16

111

S1

S0

address

001

AR

010

PC

011

16-bit Bus

DR

E

ALU

100

AC

INPR

101

IR

110

TR

OUTR

clock

2

Bus Architecture

- The three access select lines determine which

register is allowed to write to the bus at a

given time (recall that only one write at a time

is allowed) - Registers have load input signals (LD) that tell

them to read from the bus - If registers are smaller than the bus (less bits)

than unused bits are set to 0 - Some registers have additional input signals

- Increment (INR) and Clear (CLR)

- See figure 5-4, page 130 of the textbook

3

Bus Architecture

- Memory has read/write input signals that tell it

when to take data from the bus and send data to

the bus - Memory addresses (for both read and write

operations) are always specified via the Address

Register (AR) - An alternative (used in many architectures) is a

two bus system - One address bus

- One data bus

4

Bus Architecture

- Results of all ALU (arithmetic, logic, and shift

operations) are always sent to the Accumulator

(AC) register - The ALU is the only way to set values into the

accumulator except for the clear (CLR) and

increment (INR) control lines - Inputs to the ALU come from

- The Accumulator (AC)

- The Data Register (DR)

- The Input Register (INPR)

- The E output from the ALU is the carry-out

(Extended AC) bit - Many architectures pack this into a register with

other status bits such as overflow

5

Bus Architecture

- Some pairs of microoperations can be performed in

a single clock cycle - The key is to make sure they dont both try to

put data on the bus - Consider the RTL statement

- DR ? AC, AC ? DR

- This is allowed since the DR ? AC microoperation

uses the bus while the AC ? DR microoperation

does not

6

Instructions

- We said previously that there are two parts to an

instruction - Opcode

- Operand

- Realistically the two parts should be called

- Opcode

- Everything else

7

Instructions

- Three basic types

- Those that reference memory operands

- Those that reference register operands

- Those that reference I/O devices

- Again, this is only for the fictitious

architecture in the textbook but you will find

similar categorizations in real architectures

8

Memory Instructions

- There are 14 instructions in this class

- 7 direct memory address forms

- 7 indirect memory address forms

0

11

12

14

15

I

opcode

address

I 0 means direct memory address

I 1 means indirect memory address

9

Memory Instructions

Hex Code Hex Code

Symbol I 0 I 1 Description

AND 0xxx 8xxx Mem AND AC

ADD 1xxx 9xxx Mem AC

LDA 2xxx Axxx Load AC from Mem

STA 3xxx Bxxx Store AC to Mem

BUN 4xxx Cxxx Unconditional Branch

BSA 5xxx Dxxx Branch to Subroutine

ISZ 6xxx Exxx Increment and Skip if Zero

10

Register Instructions

- There are 12 instructions in this class

- They can use the operand field to specify the

register and type of operation since no memory

address is required

0

11

12

14

15

0

1

1

1

Register operation

11

Register Instructions

Symbol Hex Code Description

CLA 7800 Clear AC

CLE 7400 Clear E bit

CMA 7200 Complement AC

CME 7100 Complement E bit

CIR 7080 Circulate right AC and E

CIL 7040 Circulate left AC and E

INC 7020 Increment AC

12

Register Instructions (cont.)

Symbol Hex Code Description

SPA 7010 Skip next instruction if AC is positive

SNA 7008 Skip next instruction if AC is negative

SZA 7004 Skip next instruction if AC is 0

SZE 7002 Skip next instruction if E is 0

HLT 7001 Halt

13

I/O Instructions

- There are 6 instructions in this class

- They can use the operand field to specify the

exact operation since no memory address is

required

0

11

12

14

15

1

1

1

1

I/O operation

14

I/O Instructions

Symbol Hex Code Description

INP F800 Input character to AC

OUT F400 Output character from AC

SKI F200 Skip on input flag

SKO F100 Skip on output flag

ION F080 Interrupt on

IOF F040 Interrupt off

15

Instruction Decoding

- The control unit evaluates bits 15 12 to

determine the instruction format - At first glance it appears that there can be only

8 unique instructions since the opcode resides in

4 bits - But, additional instructions are created through

the use of the I bit and unused bits in the

operand field

16

Instruction Set Design

- To be useful, an architectures instruction set

must contain enough instructions to allow all

possible computations - Four categories are necessary

- Arithmetic, logical, shift operations

- Moving data to/from memory from/to registers

- Control such as branch and conditional checks

- Input/output

17

Instruction Set Design

- The set in the book is complete in that all the

possible operations on binary numbers can be

performed through combinations of instructions - But, the set is very inefficient in that highly

used operations require multiple instructions - This is why the Pentium instruction set is so

large and complicated it makes for efficient

programs

18

- So, how does the control unit know what to tell

the hardware what to do?

19

The Control Unit

Instruction Register (IR)

15

14 - 12

11 - 0

Other Inputs

3x8 Decoder

12

Control Unit

D7 D0

n

I

T15 T0

4x16 Decoder

Increment

Sequence Counter

Clear

Master Clock

20

Control Timing/Sequence Counter

- Due to the nature of the Fetch-Execute

instruction cycle, instructions require more than

one clock pulse to complete - But, not all instructions require the same number

of clock pulses - Thus, we divide the master clock into unique time

steps - Each time step will provide conditional input to

the logic within the control unit (recall the RTL

notation for conditional operation) - Clock division is performed by the sequence

counter - Recall that you designed one of these on the exam

21

Sequence Counter Timing

- Note that only one timing signal is a logic 1 at

any given time - The counter is modulo 16, T15 returns to T0

- The Master Clock always increments the counter

from Tn to Tn1 - A clear input resets the counter circuit back to

T0 - An increment moves the counter from Tn1 to Tn2

22

Sequence Counter Timing

- With the set of timing signals we can now

implement RTL statements such as - What does this RTL statement mean?

T0 AR ? PC

23

Instruction Cycle Revisited

- Fetch an instruction from memory

- Decode the instruction

- Read the operands from memory/registers

- Execute the instruction

- The actual implementation of each phase is

dependent on the instruction, although the fetch

and decode phases are common to all

24

Fetch and Decode

- Initially

- Something (the operating system in the case of

computers that have them, hardware in the case of

computers that dont have an OS) places the

address of the first program statement into the

Program Counter (PC) - The Sequence Counter (SC) is cleared to 0

- Program execution begins

25

Instruction Fetch

- Starting at time T0, fetch an instruction from

memory - What are the RTL statements to perform this step?

- Hint the key words are instruction and from

memory - Refer to the bus architecture pg 130 of the

textbook

26

Bus Architecture

S2

Access Select

Memory unit 4096x16

111

S1

S0

address

001

AR

010

PC

011

16-bit Bus

DR

E

ALU

100

AC

INPR

101

IR

110

TR

OUTR

clock

27

Instruction Fetch

- RTL

- Note that after fetching an instruction we always

increment the program counter

T0 AR ? PC T1 IR ? MAR, PC ? PC 1

28

Instruction Decode

- Instruction fetch took two cycles (T0 and T1) so

instruction decode starts at T2 - What are the RTL statements to perform this step?

- Hint the key words are instruction and

decode - Refer to the bus architecture and the control

unit pgs 130 and 137 of the textbook

29

Bus Architecture

S2

Access Select

Memory unit 4096x16

111

S1

S0

address

001

AR

010

PC

011

16-bit Bus

DR

E

ALU

100

AC

INPR

101

IR

110

TR

OUTR

clock

30

The Control Unit

Instruction Register (IR)

15

14 - 12

11 - 0

Other Inputs

3x8 Decoder

12

Control Unit

D7 D0

n

I

T15 T0

4x16 Decoder

Increment

Sequence Counter

Clear

Master Clock

31

Instruction Decode

- RTL

T2 D0, D7 ? Decode IR(12-14), AR ? IR(0-11), I

? IR(15)

32

Fetch and Decode

T0 AR ? PC T1 IR ? MAR, PC ? PC 1 T2 D0,

D7 ? Decode IR(12-14), AR ? IR(0-11), I ? IR(15)

- Figure 5-8 on page 140 of the textbook shows the

schematic interactions between the timing

signals, the register controls, and the bus

33

Fetch and Decode

T1

Bus

T0

Memory

- What happens at time T0?

- What happens at time T1?

- What do we need to add to perform at time T2?

111

Address

Read

AR

001

LD

PC

010

INR

IR

101

LD

Clock

34

Decoding the Instruction

- Once the instruction is fetched from memory (T0,

T1) and the opcode is passed to the decoder (T2)

the control unit must figure out what to do next

(T3) - Based on the opcode and the I bit (b15) it must

make decisions regarding operation type (memory,

register, I/O) and operand address mode (direct,

indirect) - Figure 5-9, pg 142 shows the RTL in flow chart

form

35

Decoding the Instruction

Of course, all this stuff gets implemented in

combinational logic

T0

T1

T2

0, memory reference

1, register or I/O

1, I/O

0, register

1, indirect

0, direct

T3

T3

T3

T3

36

Next Time

- We start looking at RTL for each individual

instruction - You should be reading/studying the material in

chapter 5 (were up to page 143) - Dont leave studying this material until the

night before an exam (which should be coming up

soon)

37

Homework

- 5-1, 5-2, 5-3, 5-4, 5-5, 5-6

- Due next lecture