FPGA Two Day Advanced FPGA Workshop Instructors

1 / 105

Title:

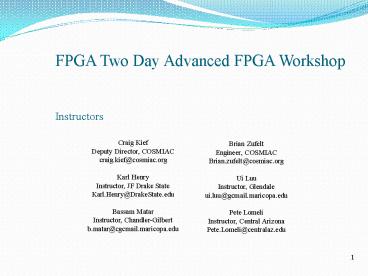

FPGA Two Day Advanced FPGA Workshop Instructors

Description:

FPGA Two Day Advanced FPGA Workshop Instructors Craig Kief Deputy Director, COSMIAC craig.kief_at_cosmiac.org Karl Henry Instructor, JF Drake State Karl.Henry_at_DrakeState.edu –

Number of Views:397

Avg rating:3.0/5.0

Title: FPGA Two Day Advanced FPGA Workshop Instructors

1

FPGA Two Day Advanced FPGA WorkshopInstructors

Craig Kief Deputy Director, COSMIAC craig.kief_at_cos

miac.org Karl Henry Instructor, JF Drake

State Karl.Henry_at_DrakeState.edu Bassam

Matar Instructor, Chandler-Gilbert

b.matar_at_cgcmail.maricopa.edu

Brian Zufelt Engineer, COSMIAC Brian.zufelt_at_cosmia

c.org Ui Luu Instructor, Glendale ui.luu_at_gcmail.m

aricopa.edu Pete Lomeli Instructor, Central

Arizona Pete.Lomeli_at_centralaz.edu

1

2

Introductions

- Who are you?

- Where are you from?

- What do you want to learn from this?

- Where are the objectives?

3

Labs we will cover

- Spin up

- Counter

- Testbench

- FSM

- Seq Det

- IP Cores

4

Why we are here again

5

Method Immersive hands-on design for every

student

Students learn more, faster, and better with

unrestricted access to design tools

overall learning improves when applied design

skills taught early overall performance

improves when design skills used frequently and

they like it

results published in 2008 and 2009 ASEE

proceedings

I never teach my pupils I only attempt to

provide the conditions in which they can learn.

Albert Einstein

6

Technology keeps moving forward faster get on

the train or be left behind

- In a meeting the first week in June, Xilinx

announced the following - The new Virtex 7 devices use approximately 20

watts - They are actually four chips on a single chip

connected with an interposer - The contain approximately 6.8 billion transistors

7

Low-cost kits and Free CAD toolsfor every

engineering student

Terasic DE0 Altera Cyclone III 79

Digilent Basys2 Xilinx Spartan 3E 59

Digilent Nexys2 Xilinx Spartan 3E 99

Terasic DE1 Altera Cyclone II 125

No Lab Required! Students work on real designs at

a time and place of their choosing

8

FPGAs Across the Curriculum

9

Please interrupt and ask questions

10

Overview

- All Xilinx FPGAs contain the same basic resources

- Logic Resources

- Slices (grouped into CLBs)

- Contain combinatorial logic and register

resources - Memory

- Multipliers

- Interconnect Resources

- Programmable interconnect

- IOBs

- Interface between the FPGA and the outside world

- Other resources

- Global clock buffers

- Boundary scan logic

11

What makes up an FPGA?

- Groups of Slices make up a Complex Logic Block

(CLB) - Each slice has four outputs

- Two registered outputs,

two non-registered outputs

12

Spartan-3E Architecture

CLB

Slice

13

DESIGN Hardware Descriptive Languages (HDL)

VHDL VERILOG C SYSGEN Schematic

Capture EDK IP Cores Limitless Tools

SYNTHESIS Many files in one file out One

File EDIF Syntax Checking Less Tool Choices

IMPLEMENTATION PLACE AND ROUTE Place Logic onto

the CLBs Route IOB CLB IOB UCF

EDIF .BIT ONE TOOL

PROGRAM JTAG PROGRAM FPGA PROM ADEPT vs

JTAG Chain

BEHAVIORAL SIMULATION

TIMING SIMULATION

14

Design

15

How are FPGA projects Designed?

- There are many different methodolgies for

programming (or designing) with FPGAs - Hardware Descriptive Language (HDL)

- VHDL

- Verilog

- Schematic Capture

- C Code

- EDK

- System Generator

16

VHDL Code

The title of the article is "Analysis of the

programmable logic usage and assurace survey

results revision 10.1, sept 25,2002Glenn

research center, Cleveland, Ohio.QuoteIt is a

serious mistake to equate VHDL programming to

software. At best it is firmware, but for the

most part there isn't a good name for programming

FPGA logic. In a high performance design like

ours, the minute you forget that you are

designing hardware and think you are writing

software, you fail.

17

VHDL Code

Forest Level View

18

Architecture Declaration

19

VHDL Recap and Objects

20

Variables

21

Not limitless Operators

22

Available Operators

23

Picking off bits

24

Data types, operators and conversion

25

CASE STATEMENT

00 01 10 11

- SELECTED SIGNAL ASSIGNMENT

SELECT X WHEN 00, Y WHEN 01, Z WHEN

10, Z WHEN OTHERS

USED WHEN NO PRIORITY EQUIVALENT TO CASE

STATEMENT (get code)

26

IF STATEMENT

X

0 1

Y

OUT

0 1

A

Z

B

- CONDITIONAL SIGNAL ASSIGNMENT

- PROCESS (X, Y, Z, A, B)

- SENSITIVITY LIST. ANYTHING READ MUST BE HERE

NOTHING HERE IS EVER ON LEFT SIDE OF ASSIGNMENT

Everything on Right hand side of assignment is

read

IF B 1 THEN OUT lt Z ELSIF A 1 OUT lt

Y ELSE OUT lt X END IF END PROCESS

PRIORITY EXISTS

27

Assignment Operators

- lt Used to assign a value to a SIGNAL

- a lt 1

- Used to assign an value to a VARIABLE,

CONSTANT, or GENERIC. Used also for establishing

initial values - constant N integer18

- gt Used to assign values to individual vector

elements or with OTHERS - display_out display_controller

- port map(

- clk gt clk,

- reset gt reset,

- q_reg lt (othersgt'0')

28

RULES

DONT USE PROCESS IF DONT HAVE TO Simple,

concurrent and selected signal assignments can be

done outside of a process. Danger of using a

process is you might get a inferred latch

(unwanted clock cycle) MULTIPLE ASSIGNMENTS TO

SAME SIGNAL, LAST ONE HOLDS FOR EVERY OUTPUT

SIGNAL THAT CAN BE ASSIGNED, ALL POSSIBLE

CONDITIONS MUST BE ADDRESSED Always assign

default values at the top of the block before

case and if statements ALL INPUT SIGNALS READ

MUST BE IN THE SENSITIVITY LIST FOR COMBINATIONAL

LOGIC FOR SEQUENTIAL USE CLK/RESET

29

I wish to help all of you to begin teaching FPGAs

30

Start the Learning

The key from this workshop is to learn what you

need to know to successfully teach with FPGAs

31

Get Started!

- Create a 2 input AND gate! Create the VHDL,

Testbench, UCF and download it

- Steps

- Start ISE

- New Source VHDL Module

- Use Wizard to do I/O

- New Source Create UCF for pin assignment

- New Source VHDL Testbench

- Simulate

- Program FPGA

32

Things to discuss before the labs

- Slow clock

- Using it, changing it for simulations

- Debouncing

- Alex material

- ISE 7 vs 14

33

Labs we will cover

- Spin up

- Counter

- Testbench

- FSM

- Seq Det

- IP Cores

34

Lab 6 - Counters

- Download ISE 14.1 version of Lab 6 from

http//cosmiac.org/Projects_FPGA.html - Create New Project

- Add Source Files

- counter.vhd

- display_controller.vhd

- counter_TB.vhd

- counter4.ucf

- Download and Review FPGA Reference Manual

- Change clk pin assignment as needed

- Change UCF pin assignments as needed

- Review vhd and ucf code

- Review Testbench

35

Counters - Eloquent Example

36

Counter

37

Counter cont. (2)

38

Counter cont. (3)

39

Display_Controller

40

Display_Controller cont. (2)

41

Display_Controller cont. (3)

42

UCF Spartan 6 pins

We are using a Nexys 2, Spartan-3 for this class.

We will need to change the pin assignments using

the diagram.

43

Labs we will cover

- Spin up

- Counter

- Testbench

- FSM

- Seq Det

- IP Cores

44

Autogenerated Test Benches

- Build a module test a module, ., build a system

of modules and test the system - Excellent job for technician or junior engineer

- Creating the framework of the test bench is easy

and painless - Need to have directory of files and test benches

and need to be able to quickly pick them out and

mate the source file to its test file

45

Counter Test Bench - 1

46

Counter Test Bench - 2

47

Counter Test Bench - 3

48

Counter Test Bench - 4

49

Labs we will cover

- Spin up

- Counter

- Testbench

- FSM

- Seq Det

- IP Cores

50

LAB 10Finite State Machine (FSM)

Ui Luu Glendale Community College

Bassam Matar Chandler-Gilbert Community College

51

Moore vs. Mealy State Machines

52

Learning Objectives

- Create a top-level HDL structure

- Write VHDL code to describe a Finite State

Machine - Apply VHDL codes previously developed in workshop

1 (source codes are provided in this lab

template) - (TIMER_DISPLAY.vhd, MEM16.vhd, SECURITY.ucf

module) for timer display - Implement INDICATORS.vhd (to provide visual

feedback for NEXYS2 on board switches buttons) - Verify system operations using NEXYS2 evaluation

board

53

Security Monitor System I/O

54

Security System State Diagram

55

Always start with a block diagram or dry erase

board before you start to write your VHDL

56

TIMER_DISPLAY Module

- TIMER_DISPLAY module objectives

- Provides 1 second CLK_DIV signal to Finite State

Machine - Provides control signals to display timer using

NEXYS2 onboard 7-segment LED display

57

CLK_DIV signal

- Functional Requirement

- Provides 1 second CLK_DIV signal to Finite

State Machine - Code Implementation

- process (CLK,REG) begin

- if rising_edge(CLK) then

- REG lt REG 1 CLK_DIV_INTlt'0'

- end if

- if REG X"2FAF080" then

- -- For 1 Hz use X"2FAF080" 50,000,000

(Decimal) - -- 50 MHz / 50,000,000 1 Hz

- CLK_DIV_INTlt'1'

- REGltX"0000000" --would be cleaner with

others - end if

- end process

58

TIMER_DISPLAY Functional Description

- When RUN_TIMER (from FSM) 1

- Timer counts up at 1 second rate

- Display the timer count at 7-Segment LED

- When RUN_TIMER 0

- Timer resets to 0

59

TIMER_DISPLAY Implementation(Note This

implementation was covered in Workshop May,2011)

- process (CLK,CLK_DIV_INT,RUN_TIMER)

- begin

- if RUN_TIMER '0' then

- Q_INT lt (others gt '0')

- elsif rising_edge(CLK) then

- if (CLK_DIV_INT'1') then -- Note

CLK_DIV_INT provides 1-second clock - Q_INT lt Q_INT '1'

- end if

- end if

- end process

- -- Outputs

- ADDR(3 downto 0) lt Q_INT (3 downto 0)

- ANODE_CONTROL lt "1110" -- Enable 1st digit

only, active Low - CLK_DIV ltCLK_DIV_INT

60

Review NEXYS2 I/O Device(Ref. Nexys2_m.pdf)

Note the difference

61

MEM16.vhd

- entity MEM16 is

- Port ( ADDR in STD_LOGIC_VECTOR (3 downto

0) - DATA out STD_LOGIC_VECTOR (7 downto

0)) - end MEM16

- architecture Behavioral of MEM16 is

- type ROM_ARRAY is array (0 to 15) of

std_logic_vector(7 downto 0) - constant MY_ROM ROM_ARRAY (

- -- Cathode Control for 7-SEGMENT LED Digit

(0-F) - 0 gt X"03", --0 note Cathode control is

active Low - 1 gt X"9F", --1

- 2 gt X"25", --2

- 3 gt X"0D", --3

- 4 gt X"99", --4

- 5 gt X"49", --5

- 6 gt X"41", --6

- 7 gt X"1F", --7

- 8 gt X"01", --8

- 9 gt X"09", --9

a 1

4 10011001

b 0

f 0

g 0

e 1

c 0

d 1

DP 1

62

FSM / IO port assignments(Reference System

Block Diagram)

- entity FSM is

- Port ( CLK in STD_LOGIC

- CLK_DIVin STD_LOGIC

- ARM in STD_LOGIC

- FRONT_DOOR in STD_LOGIC

- REAR_DOOR in STD_LOGIC

- WINDOW in STD_LOGIC

- RUN_TIMERout STD_LOGIC

- SIREN out STD_LOGIC)

- end FSM

63

Type Signal names Declarations

- type SECURITY_STATE is (ARMED,DISARMED,WAIT_DELAY,

ALARM) - signal CURR_STATE,NEXT_STATE SECURITY_STATE

- signal START_COUNT,COUNT_DONE std_logic

- signal SENSORSstd_logic_vector (2 downto 0)

--combine inputs - signal TIMER_CNTR std_logic_vector (2 downto 0)

(others gt '0')

64

FSM / Reading Sensors SYNC Process

- SENSORS lt FRONT_DOOR REAR_DOOR WINDOW

- SYNC process (CLK,ARM)

- begin

- if ARM '0' then

- CURR_STATE lt DISARMED

- elsif rising_edge (CLK) then

- CURR_STATE lt NEXT_STATE

- end if

- end process SYNC

concatenation New State each clock cycle

65

Implement Security System State Diagram (Figure

2)

- STATE_MACHINE process (CURR_STATE,SENSORS,ARM,COU

NT_DONE) - begin

- START_COUNT lt '0' -- establish default

- case (CURR_STATE) is

- when DISARMED gt

- if ARM '1' then

- NEXT_STATE lt ARMED

- else NEXT_STATE lt DISARMED

- end if

- -- Output

- SIREN lt '0'

- RUN_TIMER lt '0'

- when ARMED gt

- if (SENSORS / "000") then

- NEXT_STATE lt WAIT_DELAY

- else NEXT_STATE lt ARMED

- end if

Four States

66

DELAY_TIMER Process

- DELAY_TIMER process(CLK_DIV,CURR_STATE,START_COUN

T,TIMER_CNTR) - begin

- COUNT_DONE lt '0' -- default value

- if (rising_edge (CLK_DIV) and (START_COUNT

'1')) then - TIMER_CNTR lt TIMER_CNTR 1

- end if

- -- Note START_COUNT is set to 1 by the

STATE_MACHINE when CURR_STATE WAIT_DELAY - if (CURR_STATE/WAIT_DELAY) then -- Note

/ means NOT equal to - TIMER_CNTR lt "000"

- end if

- if (TIMER_CNTR "111") then -- Note this timer

times out at 7 seconds just for convenience - COUNT_DONE lt '1'

- end if

- end process DELAY_TIMER

67

INDICATORS.vhd (provides visual feedback for

NEXYS2 on board switches and buttons)

- entity INDICATORS is

- Port ( ARM in STD_LOGIC

- FRONT_DOOR in STD_LOGIC

- REAR_DOOR in STD_LOGIC

- WINDOW in STD_LOGIC

- ARM_SIG out STD_LOGIC

- FRONT_DOOR_SIG out STD_LOGIC

- REAR_DOOR_SIG out STD_LOGIC

- WINDOW_SIG out STD_LOGIC)

- end INDICATORS

- architecture Behavioral of INDICATORS is

- begin

- ARM_SIGltARM

- FRONT_DOOR_SIG lt FRONT_DOOR

- REAR_DOOR_SIG lt REAR_DOOR

68

SECURITY.ucf (I/O assignments for NEXYS2-1200)

- SECURITY.ucf

- 7/6/2011 Operation verified with NEXYS2-1200

- NET "CLK" LOC B8

- NET "ARM" LOC G18 Switch 0

- NET "FRONT_DOOR" LOC H13 Button 3

- NET "REAR_DOOR" LOC E18 Button 2

- NET "WINDOW" LOC D18 Button 1

- NET "ARM_IND" LOC J14 LED 0

- NET "FRONT_DOOR_IND" LOC K14 LED3

- NET "REAR_DOOR_IND" LOC K15 LED2

- NET "WINDOW_IND" LOC J15 LED1

- NET "CATHODE0" LOC C17 DP

- NET "CATHODE1" LOC H14 CG

- NET "CATHODE2" LOC J17 CF

69

Hands On Practice(Work in Team of 2)

- Download / Copy

- VHDL-SecurityStateMachine-Starter(NEXYS2-1200)

project folder to your desktop - Follow Lab 10 Finite State Machine (FSM)

Instructions - Verify the Security State Machine operates as

prescribed - Demonstrate to your lab coordinator

70

Sample Solution

- For reference, Sample solution is available at

project Folder - VHDL-SecurityStateMachine-SampleSolution(NEXYS2-1

200)

71

Labs we will cover

- Spin up

- Counter

- Testbench

- FSM

- Seq Det

- IP Cores

72

Sequence Detectors

73

Sequence Detectors

- Practical applications

- Facial recognition

- Searching for correct patterns

- DSP

74

Labs we will cover

- Spin up

- Counter

- Testbench

- FSM

- Seq Det

- IP Cores

75

IP Cores

- What are Cores?

- CoreGen Wizard

76

IP Cores

77

IP Cores Datasheets

78

IP Cores Lessons Learned

- Dont assume you know the way the core will work

- Build a project with only the core in it and test

it alone until you are sure you know how it works - If you cant see any of the cores

- Setting environment variable XIL_CG_LOAD_ALL_FAMIL

IEStrue Especially for 14.4.

79

Other STUFF

80

Obtaining, licensing and service contract with

Xilinx

- If you decide to go with Xilinx, we can help you

the most (with currently available resources) - Register with XUP

- Get software

- Pay annual fee

- Put one person in charge

81

Synthesizing Designs

1

Generate a netlist file using XST (Xilinx

Synthesis Technology)

Highlight HDLSources

2

Double-click to Synthesize

- Synthesis Processes and Analysis

- Access report

- View Schematics (RTL or Technology)

- Check syntax

- Generate Post-Synthesis Simulation Model

82

Implementation

Netlist GeneratedFrom Synthesis

- Consists of three phases

- Translate Merge multiple design files into a

single netlist - Map Group logical symbols from the netlist

(gates) into physical components (slices and

IOBs) - Place Route Place components onto the chip,

connect the components, and extract timing data

into reports - Access Xilinx reports and tools at each phase

- Timing Analyzer, Floorplanner, FPGA Editor, XPower

. . .

Implement

. . .

Translate

Map

Place Route

. . .

83

Device Implementation Place Route

Design Flow

Specification

Gates of the design ...

libraries

HDL

netlist

... are placed ...

... and routed

Verification

test vectors

Implementation

Translate

Fitting/ Place Route

84

Simulations

85

Configuring FPGAs

1

Highlight source file

- Configure FPGAs from computer

- Use iMPACT to download bitstream from computer to

FPGA via Xilinx download cable (ie. Platform USB) - Configure FPGAs from External Memory

- Xilinx Platform Flash

- Use iMPACT to generate PROM file and download to

PROM using Xilinx download cable - Generic Parallel PROM

- Use iMPACT (or in our case Adept) to generate

PROM file - no support for programming - Compact Flash (Xilinx System ACE required)

- Use iMPACT to generate SysACE file - no support

for programming

2

Double-click to generate .bit

3

Double-click to invoke iMPACT programming tools

86

JTAG IEEE Standard

- Six Signals

- TMS

- TCK

- TDI

- TDO

- Pwr

- Gnd

87

Demo Impact

88

Webpack

- This is the really great benefit to students.

Xilinx makes a free version of their ISE

software. This means that students can do entire

projects at home and only come to the lab to

demo. - http//www.xilinx.com/ise/logic_design_prod/webpac

k.htm - Altera has a similar product

89

Webpack vs Full Version

90

Webpack

91

Plan Ahead

- In the near future Xilinx ISE will transition

from the traditional Project Navigator to Plan

Ahead. - Easier integration of various design types

92

PlanAhead

- Very similar to project navigator

93

EDK

- Very similar to project navigator

94

Default Locations for SW

- When you are setting up the software, regardless

of if it is at the lab or at home, only install

the software at the default locations.

95

Licensing

- Node Lock (Ethernet versus Hard Drive Serial

Number) - Server Licensing

- Student versus Lab

96

Digilent (cont.)

- Clints boards

97

Educational Materials Available

- Clints web site www.eecs.wsu.edu/ee214

- Digilent website www.digilentinc.com

- Our XUP site www.ece.unm.edu/vhdl

- XUP site

- www.cosmiac.org

- Quick start tutorials launch within ISE

- What we are developing!

98

Educational Materials Available

http//www.digilentinc.com/classroom/realdigital/

99

Donated SW and HW

- Software

- Register with XUP

- Mention working with us

- Dont chase releases

- Hardware

- 10 boards

100

Beginners and Advanced Workshops

We offer a series of free two-day workshops for

instructors and professors to allow them to be

able to learn the basics of establishing FPGA

programs at their schools Coming in the Fall of

2012 Beginners Microcontroller workshops!

101

Collaboration

We do collaborations very well ATE proposals due

October 2013

102

Help with Writing Proposals

www.teachingtechnicians.org Hi Craig, By cc

of this message, I am asking Charlotte Forrest

(Mentor-Connect Project Manager) to provide you

with information that can be shared at your next

ATE workshop. Thanks so much for asking! We

will start work with a new cohort of potential

grantees in fall 2013. We are currently working

with a cohort of 20 colleges that were selected

in fall 2012. The cycle starts with an

orientation webinar in September and is followed

by an application process. Those selected

receive considerable help in preparing a

successful proposal and are paired with an

experience ATE mentor for all of the months

leading up to their proposal submission. The

program serves those who have not previously

received NSF ATE funding that was awarded

directly to their institution within the past 10

years. If they have been a partner on a grant

awarded to another institution, they are

eligible. If their institution is a branch of a

larger institution but there is a chief academic

officer for their branch campus, they are

eligible even if another branch of the

organization has been a grantee (for example, the

Ivy Tech system in Indiana where college

locations within the system have their own

administration). Also, this opportunity is for

associate degree granting institutions (primarily

two-year technical and community colleges).

Again, many thanks for contacting me and for

helping spread the word about this

opportunity. Elaine

103

Deploying Curriculum

- Website http//cosmiac.org/FPGA.html

104

Conclusions

105

Painful survey

We need your help in statistics. We will be

contacting you!