Frequency Divider Design Example - PowerPoint PPT Presentation

Title:

Frequency Divider Design Example

Description:

Title: Slide 1 Author: Yu_Lin Last modified by: presenter Created Date: 4/15/2005 8:23:36 PM Document presentation format: On-screen Show Company: Iowa State University – PowerPoint PPT presentation

Number of Views:331

Avg rating:3.0/5.0

Title: Frequency Divider Design Example

1

(No Transcript)

2

Frequency Divider Design Example

- Yu Lin

3

Frequency Divider approaches(1)

- Analog approaches

- Regenerative injection-locked frequency divider

- Basic mixer theory fofin-fLO

- Examples

- If fofLO, then fin2fo

- If third harmonic of LO, fLO3fo

4

Frequency Divider approaches(2)

- Digital logic approaches

- Static Logic bistable circuit as memory

- Divider/2 Examples

- Edge-Triggered DFF.

5

- Eg 2. JK FF

- JK1, toggle

THlt (tud1, tdd2) lt T

6

Frequency Divider approaches(3)

- Digital logic approaches

- Dynamic Logic

- No dedicated bistable circuit

- Parasitic cap between node as storage element

- Compared to static approach

- Faster

- Simpler implementation

- Frequency has lower limit

7

Design of divide/2

- SiGe BiCMOS

- Dynamic frequency divider

- Input frequency 40GHz

- /-20 input frequency range (32GHz48GHz)

- Work from 0 ?C to 100 ?C at 40GHz

- Input 200mv

- Output 200mV

Reinhold, M. Dorschky, C. Rose, E. Pullela,

R. Mayer, P. Kunz, F. Baeyens, Y. Link, T.

Mattia, J.-P., A fully integrated 40-Gb/s clock

and data recovery IC with 14 DEMUX in SiGe

technology, Solid-State Circuits, IEEE Journal of

Vol.36, Issue 12, Dec. 2001 Page(s)1937 - 1945

8

(No Transcript)

9

0.5Tlt (tud1, tdd2) lt T

10

- Four-phase clock

- Fully differential

- 0?C or 90?C phase-shifted

11

Design key points

- Find optimal current density for highest ft

- Choose appropriate current for the current

sources - Choose appropriate resistors to set up good

quiescent points - Appropriate resistance and parasitic capacitance,

delay time (tdd1 and tud2) around 0.75T

12

Design key points(2)

- Resistances are related to the quiescent point

and input frequency range, key point of robust

design - Added buffer to do level shifting, improve the

driving capability and adjust gain - Driving capability increases when increase the

current

13

Simulation results(1)

The output of divider core at 27C with normal

model with 28G Hz input

14

Simulation results(2)

The output of divider core at 27C with normal

model with 40G Hz input

15

Simulation results(3)

The output of divider core at 27C with normal

model with 53G Hz input

16

Simulation results(4)

Frequency range (GHz) Slow Normal Fast

0?C 26-55 29-55 39-76

27?C 27-51 28-53 36-70

100?C 27-42 24-44 33-56

17

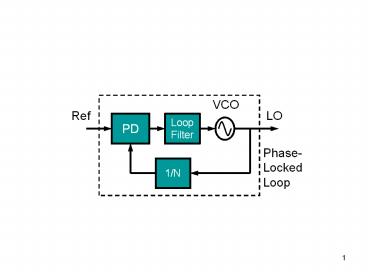

VCO Design Example

- Chao Su

Chao Su Thoka, S. Kee-Chee Tiew Geiger, R.L.,

A 40 GHz modified-Colpitts voltage controlled

oscillator with increased tuning range, ISCAS

'03. Proceedings of the 2003 International

Symposium onVolume 1, 25-28 May 2003

Page(s)I-717 - I-720 vol.1

18

- A system with characteristic

- If

- It will oscillate at

19

Basic Colpitts VCO

Oscillate when

Assume for inductor

Then

Where

20

- For given L, gm, C?,

- Wide frequency range can be obtained with high Q

by tuning CL - High Q can be achieved with reduction of

effective GP

21

Modified Colpitts Circuit

- Achieve negative resistance by cross-coupled BJT

22

(No Transcript)

23

Simulation results

24

Divide/2

Modified Colpitts VCO

25

Measurement Results

- Three VCOs with three different inductors

- fVCO(2831GHz)

- fd/2(14.816GHz)

- Tuning range smaller compared to simulation