Built-In Self-Test and Calibration of Mixed-Signal Devices - PowerPoint PPT Presentation

Title:

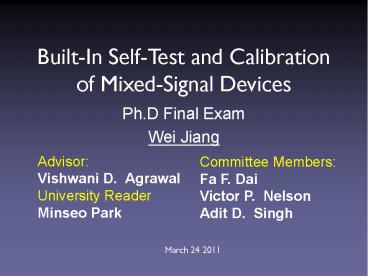

Built-In Self-Test and Calibration of Mixed-Signal Devices

Description:

Built-In Self-Test and Calibration of Mixed-Signal Devices Ph.D Final Exam Wei Jiang Advisor: Vishwani D. Agrawal University Reader Minseo Park Committee Members: – PowerPoint PPT presentation

Number of Views:284

Avg rating:3.0/5.0

Title: Built-In Self-Test and Calibration of Mixed-Signal Devices

1

Built-In Self-Test and Calibration of

Mixed-Signal Devices

- Ph.D Final Exam

- Wei Jiang

Advisor Vishwani D. Agrawal University

Reader Minseo Park

Committee Members Fa F. Dai Victor P.

Nelson Adit D. Singh

March 24 2011

2

Outline

- Introduction

- Background

- BIST Architecture for Mixed-Signal Devices

- Overview of Proposed Architecture

- Test of DAC/ADC

- Calibration of DAC

- Sigma-Delta Modulation

- Polynomial Fitting Algorithm

- Conclusion

3

Motivation

- Digital BIST techniques

- Defect-oriented

- Logic BIST, scan chain, boundary scan, JTAG, etc

- Mixed-Signal BIST techniques

- Specification-oriented

- No universally accepted standard

- Issues

- Parameter deviation

- Process variation

4

Approach

- Problem

- Design a post-fabrication variation-tolerant

process-independent technique for mixed-signal

devices - Solution

- Test and characterize mixed-signal devices using

digital circuitry - Use DSP as BIST controller for test pattern

generation (TPG) and output data analysis (ORA) - Calibrate mixed-signal devices

5

Mixed-Signal Devices

- Both digital and analog circuitry in single die

- DSP usually embedded for data processing

- Analog circuitry controllable by digital part

- Converters

- Analog-to-digital converter (ADC)

- Flash ADC, successive-approximation ADC,

Pipeline ADC, Sigma-Delta ADC - Digital-to-analog converter (DAC)

- PWM/Oversampling DAC, Binary-weighted DAC

6

Testing of Mixed-Signal Devices

- Both digital and analog circuitry need test

- Defects and faults

- Catastrophic faults (hard faults)

- Parametric faults (soft faults)

- Test approaches

- Functional test (specification oriented)

- Structural test (defect oriented)

7

Digital BIST

- Conventional logic BIST technology

- LFSR-based random test Scan-based deterministic

test - DSP can be TPG and ORA

- Digital circuitry must be fault-free before being

used for mixed-signal test - May be hardware or software based

8

Faulty Mixed-Signal Circuitry

- Good circuitry

- All parameters and characteristics are within

pre-defined specified range - Fault-tolerance factor

- Post-fabrication and software-controllable

- Trade-off between fault-tolerance of parameter

deviation and calibration resolution - Larger value for wider fixing range smaller one

for better fixing results - Fault-tolerance factor may vary for different

applications

9

A Basic Digital BIST Architecture

10

Challenges

- Analog circuitry

- No convincing fault model

- Difficult to identify faults

- Device parameters more susceptible to process

variation than digital circuitry - Fault-free behavior based on a known range of

acceptable values for component parameters - Large statistical process variation effects in

deep sub-micron MOSFET devices

11

Process Variation

- Parameter variation in nanoscale process

- Yield, reliability and cost

- Feature size scaling down and performance

improvement - Effects on digital and analog circuitry

- Analog circuitry more affected by process

variation - Parameter deviation severed in nanoscale process

- System performance degraded when parameter

deviation exceeds beyond tolerant limits

12

Outline

- Introduction

- Background

- BIST Architecture for Mixed-Signal Devices

- Overview of Proposed Architecture

- Test of DAC/ADC

- Calibration of DAC

- Sigma-Delta Modulation

- Polynomial Fitting Algorithm

- Conclusion

13

Resolution and Non-linearity Error

- Resolution N-bit

- Least significant bit (LSB)

- Non-linearity errors

- Differential non-linearity (DNL)

- Integral non-linearity (INL)

14

Non-linearity Error of ADC

- Signal values at lower and upper edges of each

codes

15

Non-linearity Error of ADC/DAC

Non-linearity error

Non-linearity error

16

Noise and SNR

17

Outline

- Introduction

- Background

- BIST Architecture for Mixed-Signal Devices

- Overview of Proposed Architecture

- Test of DAC/ADC

- Calibration of DAC

- Sigma-Delta Modulation

- Polynomial Fitting Algorithm

- Conclusion

18

Typical Mixed-Signal Architecture

19

Mixed-Signal System Test Architecture

F. F. Dai and C. E. Stroud, Analog and

Mixed-Signal Test Architectures, Chapter 15, p.

722 in System-on-Chip Test Architectures

Nanometer Design for Testability, Morgan

Kaufmann, 2008.

20

Test Architecture

- Digital system

- Digital I/O, digital loopback

- Digital signal processor (DSP)

- TPG and ORA and test control unit

- Mixed-signal system

- DAC and ADC, Analog loopback

- Analog system

- Analog circuitry

- Analog signal I/O, analog I/O loopback

21

Available Testing Approaches

- Servo-loop Method

- Oscillation BIST Method

- Sigma-Delta Testing Method

- FFT-based Testing Method

- Histogram Testing Method

- Widely used for testing of on-chip ADC/DAC

- Need large amount of samples and slow-gain

current source - Unsuitable for high-resolution converters

22

Outline

- Introduction

- Background

- BIST Architecture for Mixed-Signal Devices

- Overview of Proposed Architecture

- Test of DAC/ADC

- Calibration of DAC

- Sigma-Delta Modulation

- Polynomial Fitting Algorithm

- Conclusion

23

Simplified Mixed-Signal System

24

Proposed Approach

25

Testing Components

- Analog Signal Generator (ASG)

- Linear ramp signals

- Sinusoidal signals

- Measuring ADC (m-ADC)

- High-resolution and high linearity

- First-order single-bit Sigma-Delta ADC

- Dithering DAC (d-DAC)

- Low resolution and low cost

- Output voltage specified error-tolerant range

- Polynomial evaluation unit

26

Design of Ramp Signal Generator

?VVth

?V

I/19.5

Range 0 v Vdd-?V

I

I

Switch for resetting ramp

Carefully chosen to make ?V 0

27

Sinusoidal Testing Signal

- More complex design

- Used for dynamic testing (non-linearity (IP3),

dynamic range, harmonic distortion) - Fast Fourier Transformation (FFT) by DSP required

- Optional in the proposed BIST approach

28

Testing Components

- Measuring ADC (m-ADC)

- First-order single-bit Sigma-Delta ADC

- ENOB determined by oversampling ratio

- Dithering DAC (d-DAC)

- Low resolution DAC binary-weighted

- Fault-tolerance factor

29

Outline

- Introduction

- Background

- BIST Architecture for Mixed-Signal Devices

- Overview of Proposed Architecture

- Test of DAC/ADC

- Calibration of DAC

- Sigma-Delta Modulation

- Polynomial Fitting Algorithm

- Conclusion

30

Testing Steps

- Diagnosis of testing components

- Testing of on-chip ADC using analog testing

signals - Testing of on-chip DAC using embedded DSP and

measuring ADC - Calibration of on-chip DAC using dithering DAC

- Validation of DAC calibration results using

on-chip ADC/DAC

31

Diagnosis of Testing Components

Assume non-linearities in signal generator and

d-DAC do NOT match

32

Diagnosis of Testing Components

- ASG and m-ADC

- Analog signal generated usually linear ramp

- m-ADC measures analog signals

- DSP determines gain and offset of measurements

- d-DAC and m-ADC

- DSP makes on-chip DAC output constant 0

- DSP generates digital test patterns usually

linear ramp - m-ADC measures d-DAC outputs

- DSP determines gain and offset of measurements

- Only situation that fault undetected

- ASG and d-DAC have exactly same non-linearity

errors

33

Testing of ADC

- Similar to histogram testing method

34

Testing of ADC

- Divided full-range of ADC codes into two

equal-size sections - Sum up measurements of each section

- Lower bound M(0) and upper bound M(K) are

discarded because of possible out-of-range

measurements

35

Estimating Coefficients

36

Detailed Steps

- Reset ramp testing signal generator

- Detect first non-zero ADC output (lower-bound of

samples) - Measure all subsequent samples

- Stop at the maximum ADC output (upper-bound of

samples) - DSP collects all valid measurements and start to

processing data - Divide measured samples into two equal-size parts

- Accumulate measurements of each part to obtain

two sums - Calculate two syndromes from two sums

- Calculate two estimated coefficients of the

linear ramp function - (Optional) Compare each measured data to

estimated one from ramp function

37

Simulation Results

- DNL and INL

- Estimation results

38

Other considerations

- Minimal number of samples

- More samples, less quantization noise, more

accurate estimation - Not all codes need to be sampled in order to

reduce testing time - At least 2N-2 samples are found necessary in

practice - The same idea may be used with low-frequency

sinusoidal testing signals instead of ramp signal - More overhead and complexities with sinusoidal

generator

39

Testing of DAC

- DSP as both TPG and ORA

40

Test of DAC

41

Components

- Digital circuitry (including DSP) as BIST control

unit - Test pattern generation (TPG) and output response

analysis (ORA) - Measuring ADC

- First-order 1-bit Sigma-Delta modulator

- Digital low-pass filter

- Measuring outputs of DAC-under-test

- Dither DAC (not used)

- Low resolution DAC

- Generating correcting signal for calibration

- Calibrated DAC for test of ADC-under-test

- ADC Polynomial Fix (not used during testing)

- Digital process to revise ADC output codes

42

Polynomial Fitting Algorithm

- Introduced by Sunter et al. in ITC97 and A. Roy

et al. in ITC02 - Summary

- Divide DAC transfer function into four sections

- Combine function outputs of each section (S0, S1,

S2, S3) - Calculate four coefficients (b0, b1, b2, b3) by

easily-generated equations

43

Third-order Polynomial

- Offset

- Gain

- And Harmonic Distortion

44

Simulation Results

- INL of 14-bit DAC

- Results of fitting polynomial

Oversampling ratio for m-ADC

45

Outline

- Introduction

- Background

- BIST Architecture for Mixed-Signal Devices

- Overview of Proposed Architecture

- Test of DAC/ADC

- Calibration of DAC

- Sigma-Delta Modulation

- Polynomial Fitting Algorithm

- Conclusion

46

Calibration of DAC

- The output of calibrated DAC can be considered as

linear

47

Dithering DAC

Estimated DAC resolution (bits)

Oversampling ratio (OSR)

- low-resolution DAC

- Better linearity output with DEM

- Must be tested by measuring ADC before test of

on-chip mixed-signal devices

a1

2

3

17bits

Resolution of dithering-DAC (bits)

48

Polynomial Evaluation

- Either hardware or software implementation

- Hardware Implementation

- Faster and DSP not occupied

- High overhead due to huge block of digital

multiply circuit - Software Implementation

- DSP drives both on-chip DAC and dithering DAC

with calculated value - Performance penalty

49

Simulation Results

- d-DAC errors

- Calibration results

50

Verification of ADC/DAC

OPTIONAL

51

Outline

- Introduction

- Background

- BIST Architecture for Mixed-Signal Devices

- Overview of Proposed Architecture

- Test of DAC/ADC

- Calibration of DAC

- Sigma-Delta Modulation

- Polynomial Fitting Algorithm

- Conclusion

52

Measuring ADC

- First-order single-bit sigma-delta ADC

- Diagnosis performed before mixed-signal test

- In-band quantization noise moved up due to

oversampling and noise shaping - Higher-order multiple-bit Sigma-Delta ADC can

also be used

53

Sigma-Delta Modulator

- First-order single-bit

- Diagram

- Transfer function

54

Oversampling and Noise shaping

F. F. Dai and C. E. Stroud, S? Modulation for

Factional-N Synthesis Chapter 9, p. 307 in

System-on-Chip Test Architectures Nanometer

Design for Testability, Morgan Kaufmann, 2008.

55

Sigma-Delta Modulator

- Oversampling Ratio

- Signal-to-noise-distortion Ratio

- Signal-to-noise Ratio

- First-order

56

Sigma-Delta Modulator

- Second-order

- Higher order

57

Select Proper Order

SNR (LSB)

Third-order

Second-order

17-bit ENOB104.1LSB

First-order

Oversampling ratio (OSR)

58

Multiple Bits

- N NOB of quantizer

- n order of S? modulator

59

Outline

- Introduction

- Background

- BIST Architecture for Mixed-Signal Devices

- Overview of Proposed Architecture

- Test of DAC/ADC

- Calibration of DAC

- Sigma-Delta Modulation

- Polynomial Fitting Algorithm

- Conclusion

60

Polynomial Fitting

- Different order of fitting polynomial can be used

for various applications - Linear fitting

- Second-order fitting

- Third-order fitting

- Higher order fitting

- Computation complexity and hardware overhead

increase exponentially

61

Linear Fitting

62

Second-order Fitting

63

Second-order Fitting

64

Third-order Fitting

65

Comparison of different orders

66

Higher-Order Fitting

- Possibly better fitting result

- Impractical for hardware implementation due to

huge overhead - Expressions on calculation of coefficients can be

derived in the same way - Usually third-order polynomial fitting is

sufficient for the most applications

67

Adaptive Polynomial Fitting

- Dynamically choose polynomial degree

- Low-order polynomial

- Simple to design and implement

- Less area and performance overhead

- Large fitting error

- High-order polynomial

- Better fitting results

- More coefficients to store

- Much more complicated polynomial evaluation

circuitry design and heavy area and performance

overhead

68

Implementation

- Analog Signal Generator (ASG)

- A few transistors low overhead

- Measuring ADC (m-ADC)

- First-order 1-bit Sigma-Delta ADC low overhead

- Dithering DAC (d-DAC)

- Low resolution DAC low overhead

- Polynomial Evaluation Unit (HW)

- Multiply-accumulate Logic huge overhead

69

Truncation Error

Truncation Error (LSB) Linear Second-order Third-order Higher

4-bit 64.296 77.474 84.6201 88.622

8-bit 3.2427 5.0105 5.8187 6.2390

12-bit 0 0.28352 0.37217 0.40544

16-bit 0 0.010821 0.023578 0.025812

Truncation Error (LSB) Linear Second-order Third-order Higher

4-bit 255.30 309.60 337.97 354.91

8-bit 15.251 20.358 23.170 25.054

12-bit 0 1.2515 1.4993 1.6491

16-bit 0 0.070815 0.094711 0.10523

- 12-bit is sufficient for a10-bit DAC (above)

16-bit for 12-bit DAC (below)

70

Truncation Error

Truncation Error (LSB) Linear Second-order Third-order Higher

4-bit 1023.3 1237.9 1351.3 1419.5

8-bit 63.252 81.181 92.521 100.141

12-bit 3.2405 5.1244 5.9794 6.5742

16-bit 0 0.31280 0.37720 0.42131

20-bit 0 0.017700 0.023781 0.026617

24-bit 0 0.00067559 0.0014819 0.0016703

16-bit is sufficient for calibration of a14-bit

DAC 17-bit could be better

71

Hardware Overhead

Overhead (Gates/DFFs) Linear Linear Second-order Second-order Third-order Third-order Higher Higher

4-bit 216 38 495 87 866 153 1329 235

8-bit 357 63 863 152 1556 275 2334 430

12-bit 520 92 1281 226 2322 410 3642 643

16-bit 658 116 1646 291 3009 531 4743 837

20-bit 820 145 2064 364 3775 666 7218 1274

24-bit 959 169 2432 429 4464 788 8580 1514

Synthesized with TSMC018 library approximately

in count of NAND2/DFFX1

72

Testing Time

- Variables

- N resolution of on-chip ADC/DAC

- T sample/conversion time of ADC/DAC

- M OSR for Sigma-Delta modulator

- N resolution of d-DAC

- Example

- 14-bit ADC/DAC with 10ns conversion time

- Oversampling ratio of S? is 2000

- 6-bit d-DAC for calibration

73

Testing Time

- Diagnosis

- ASG and m-ADC Td1

- d-DAC and m-ADC Td2

- Test of ADC Tad

- Test of DAC Tda

- Verification of ADC/DAC Tv

- Total testing time

- Assume T10ns, M2000,N14, N6

- Total time 657ms

74

Outline

- Introduction

- Background

- BIST Architecture for Mixed-Signal Devices

- Overview of Proposed Architecture

- Test of DAC/ADC

- Calibration of DAC

- Sigma-Delta Modulation

- Polynomial Fitting Algorithm

- Conclusion

75

General Mixed-Signal Test

- Variation-tolerant design

- Digital controlled BIST

- Digitalized TPG/ORA

- Self-testable measuring components

- Characterization of device-under-test by DSP

- Faulty circuitry determined by characterized

parameters - Coefficients of output fix/correction signals

calculated by DSP

76

Conclusion

- A post-fabrication built-in test and calibration

approach for mixed-signal devices is proposed - This approach relies on digital circuitry and DSP

for TPG/ORA and BIST control - Digital circuitry is testable by conventional

digital testing approaches and therefore

guarantee the testability of analog circuitry - On-chip ADC/DAC are tested separately and

verified - Calibration on mixed-signal devices will

significantly reduce defects, improve die yield

and lower manufacturing cost

77

Publications

- W. Jiang and V. D. Agrawal, Built-In Test and

Calibration of DAC/ADC Using A Low-Resolution

Dithering DAC, NATW08, pp. 61-68. - W. Jiang and V. D. Agrawal, Built-in

Self-Calibration of On-Chip DAC and ADC, ITC08,

paper 32.2. - W. Jiang and V. D. Agrawal, Built-in Adaptive

Test and Calibration of DAC, NATW09, pp. 3-8. - W. Jiang and V. D. Agrawal, Designing

Variation-Tolerance in Mixed-Signal Components of

a System-on-Chip, ISCAS09, pp. 126-129. - W. Jiang and V.D. Agrawal, A DSP-Based Ramp Test

for On-Chip High-Resolution ADC, ICIT11

78

References

- M. L. Bushnell and V. D. Agrawal, Essentials of

Testing for Digital, Memory, Mixed-Signal VLSI

Circuits, Boston Springer, 2000 - F. F. Dai and C. E. Stroud, Analog and

Mixed-Signal Test Architecture, Morgan kaufmann,

2008. - S. Sunter and N. Nagi, A Simplified Polynomial

Fitting Algorithm for DAC and ADC BIST, ITC97,

pp.389-395 - A. Roy, S. Sunter et al., High Accuracy Stimulus

Generation for A/D Converter BIST, ITC02,

pp.1031-1039

79

Thank you