Potential Swiss Army Knife Applications

Title:

Potential Swiss Army Knife Applications

Description:

Digital Radios / MP3 Players (i.e. Motorola, Lucent, Texas Instruments) Digital Music Synthesis / Sampling (i.e. Yamaha, Korg) Noise Reduction (i.e. Dolby) ... –

Number of Views:34

Avg rating:3.0/5.0

Title: Potential Swiss Army Knife Applications

1

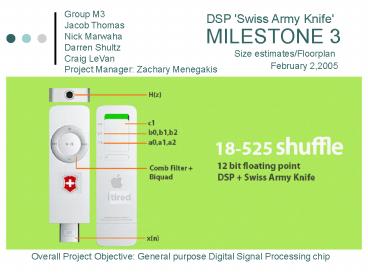

Group M3 Jacob Thomas Nick Marwaha Darren

Shultz Craig LeVan Project Manager Zachary

Menegakis

DSP 'Swiss Army Knife'

MILESTONE 3 Size estimates/Floorplan

February 2,2005

Overall Project Objective General purpose

Digital Signal Processing chip

2

STATUS

- Design Proposal (Done)

- Architecture (Done)

- Size Estimates/Floorplan/Verilog (90)

- To Be Done

- Structural Verilog Reengineering

- Control Logic

- Low-Level Modules

- Schematic

- Verification

3

MARKETING UPDATE

- How Does Our Circuit Fit Into the Bigger Picture?

- Focus on Audio/Video Applications

- Audio

- Digital Radios / MP3 Players (i.e. Motorola,

Lucent, Texas Instruments) - Digital Music Synthesis / Sampling (i.e. Yamaha,

Korg) - Noise Reduction (i.e. Dolby)

- Video

- Comb Filter to separate color and brightness

(i.e. Sony, Toshiba) - Others

- Motor Control Functions such as RPM (i.e. Ford,

GE)

4

MARKETING UPDATE cont

Highlighted Areas Contain Many Instances of our

Circuit

Key Functions used Integrators and Filters

REUSE!!!!

5

MARKETING UPDATE cont

- A Moving Averager Smoothes a Signal to Reduce

Noise

6

DESIGN DECISIONS

- Finalized bit-width to 12-bit floating point

- Based on CMU Research in Voice Recognition

- Complexity gt Our Applications in Audio and Video

- 6-bit exponent, 5-bit fraction

- Additional Precision cannot be discerned by

humans - Reduces Power Consumption

- Increased bit-width does not add to

quality/versatility - Chip Applications would benefit from low power

consumption - Size offers advantages of parallel processing to

increase speed - Serial (software) vs. Parallel (hardware)

operations

7

DESIGN DECISIONS cont

8

DESIGN DECISIONS cont

Name a0 a1 a2 b0 b1 b2 c1 N

1 Differencer 1 0 0 1 -1 0 0 x

2 Integrator 1 1 0 1 0 0 0 x

3 Leaky Integrator 1 1 0 1 0 0 0 x

4 Comb Filter 1 0 0 1 0 0 1 8

5 Bandpass Filter 1 0 -1 1 0 0 1 16

6 CIC Interpolation Filter 1 1 0 1 0 0 1 8

7 dc Bias Removal 1 a.b 0 1 -1 0 0 x

8 First-Order Equalizer 1 a.b 0 a.b 1 0 0 x

9 Audio Comb 1 0 a.b 1 0 0 0 x

10 Moving Averager 1 1 0 1/N 0 0 1 8

11 Second-Order IIR Filter 1 a.bbb a.bbb a.bbbb a.bbb a.bbb 0 x

12 First-Order Delay Network 1 a.bbb a.bbb a.bbb a.bbb 1 0 x

13 Second-Order Delay Network 1 a.bbb a.bbb a.bbb a.bbb 1 0 x

14 Real Oscillator 1 2cos(x) -1 1 0 -1 x x

15 Second-Order Equalizer 1 (a.bcos(x) a.b 1 a.bcos(x) 1/a.b 0 x

16 Real FSF, Type I 1 2cos(x) -1 ?cos(x) ?cos(x) 0 1 x/2pik

17 Real FSF, Type IV 1 2cos(x) -1 ?1 0 ?1 1 x/2pik

18 Complex FSF 1 imag 0 1 0 0 1 x/2pik

19 Quadrature Oscillator G(n) imag 0 1 0 0 x x

20 First-Order IIR Filter 1 imag 0 1 imag 0 0 x

21 Goertzel Network 1 2cos(x) -1 1 imag 0 0 x/2pik

22 Sliding DFT Network imag 1 0 1 0 0 rN x/2pik

9

FLOORPLAN

Each block is approximately 100 100 with the

exception of the possibly larger comb filter

10

FLOORPLAN alternative

11

POROSITY

- STOLEN FROM W1 2004

- (Thanks Myron Bobby)

12

SIZE ESTIMATES

- Adder 5 (200 200 100) 2500

- Mult 7 (900200) 8000

- Div 2 (1000 200) 2400

- Fmult 1 (1200) 1,200

- Misc (700 250) 2,000

- Registers 83 22 1,900

- 18,000 transistors

13

VERILOG

14

PROBLEMS QUESTIONS

- Determine Bit Width

- Floorplan Minimize Comb Filter or use

Alternative? - Should Focus Be Area or Global Routing?

- Structural Verilog

- Fix Control Logic within Basic Blocks