WCR - PowerPoint PPT Presentation

Title:

WCR

Description:

WCR #7 Nyquist rate ADC. Main design motivation: Low Power. Features: ... WCR #7 ADC: Experimental DATA. LINEARITY from Code Density Histogram (Doernberg et al. ... – PowerPoint PPT presentation

Number of Views:45

Avg rating:3.0/5.0

Title: WCR

1

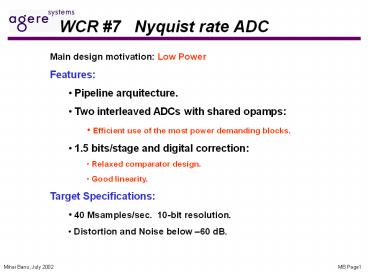

WCR 7 Nyquist rate ADC

- Main design motivation Low Power

- Features

- Pipeline arquitecture.

- Two interleaved ADCs with shared opamps

- Efficient use of the most power demanding

blocks. - 1.5 bits/stage and digital correction

- Relaxed comparator design.

- Good linearity.

- Target Specifications

- 40 Msamples/sec. 10-bit resolution.

- Distortion and Noise below 60 dB.

2

WCR 7 Nyquist rate ADC

- Pipeline ADC

- Test chip

- 4K devices

- 0.25 ?m CMOS

- SIMULATION RESULTS

- Power 12 mW _at_ 2.5 V

- (2/3 less than publishied ADCs)

- INL 0.38 LSB ? -62 dB Harm. Dist.

3

WCR 7 ADC Experimental DATA

Experimental Setup

4

WCR 7 ADC Experimental DATA

- Measured Results

- Sampling Rate 40 MHz (still running _at_ 60 MHz)

- Latency 12 cycles (300 ns)

- Power

- ADC 13.87 mW (5.55 mA _at_ 2.5V)

- Pin Drivers 1.32 mW (0.4 mA _at_ 3.3V)

- Distortion 0.3 to 0.65 LSBs

- ENOB 9.4 bits (from distortion)

5

WCR 7 ADC Experimental DATA

Single-Tone test Low Freq. (20 KHz) Very

low Distortion

6

WCR 7 ADC Experimental DATA

2-Tone test Low Freq. (100 KHz) Very

low Distortion

7

WCR 7 ADC Experimental DATA

2-Tone test High Freq. (19.5 MHz) Still good

Linearity

8

WCR 7 ADC Experimental DATA

2-Tone test High Freq. (20 MHz) 60 MHz CLK (50

Overclock) Still running

9

WCR 7 ADC Experimental DATA

LINEARITY from Code Density Histogram (Doernberg

et al.) 60 KHz input

- Too much ripples (bad code coverage?)

- Monotonic, no missing codes.

10

WCR 7 ADC Experimental DATA

LINEARITY from Code Density Histogram (Doernberg

et al.) 20 KHz input (not full-scale)

MAX INL 0.65 LSB ? (INL) 0.3 LSB

MAX DNL 0.38 LSB