Today - PowerPoint PPT Presentation

1 / 23

Title:

Today

Description:

Sync DRAM next Tuesday. Project 1 Discussion Switch Debouncing ... Synchronous DRAM (SDRAM) Access is ... RAM finds data (CPU waits in conventional DRAM) ... – PowerPoint PPT presentation

Number of Views:30

Avg rating:3.0/5.0

Title: Today

1

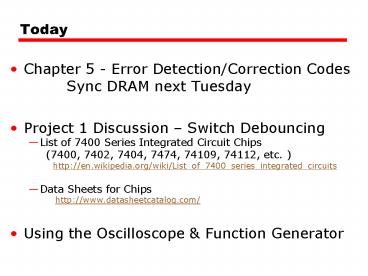

Today

- Chapter 5 - Error Detection/Correction Codes

- Sync DRAM next Tuesday

- Project 1 Discussion Switch Debouncing

- List of 7400 Series Integrated Circuit Chips

- (7400, 7402, 7404, 7474, 74109, 74112, etc.

) - http//en.wikipedia.org/wiki/List_of_740

0_series_integrated_circuits - Data Sheets for Chips

- http//www.datasheetcatalog.com/

- Using the Oscilloscope Function Generator

2

Chapter 5Internal Memory

Part II Error Detection/Correction Codes

Sync DRAM

3

Error Detection/Correction

- Errors

- Hard Failure

- Permanent defect

- Soft Error

- Random, non-destructive

- No permanent damage to memory

- Coding

- Coding can be used for

- - Error detection

- - Error correcting

- Hamming code will be explored

4

Error Correcting Code Function

5

Hamming Code Example

Visualizing

With even parity

Word

Identifying error

With Error

6

Increased word length for error correcting

7

Hamming Code Design determining K

- To store an M bit word with detection/correction

takes MK bit words - If K 1, we can detect single bit errors but not

correct them - If 2K - 1 gt M K , we can detect and

correct single bit errors, - i.e. detect an error and identify which bit

it is. - Example for M 8

- for K 3 23 1 lt 8 3

- for K 4 24 1 gt 8 4

- Therefore, choose K 4

8

Hamming Code Syndrome

If we compare the read K bits compared with the

write K bits, using an exclusive or function, the

result is called the syndrome. If the syndrome

is all zeros, there were no errors. If there is

a 1 bit somewhere, we know that represents an

error.

9

Hamming Code Syndrome Design Criteria

10

Layout of Data and Check Bits to Achieve Our

Design Criteria

C1 is a parity check on every data bit whose

position is xxx1 C1 D1 exor D2 exor D4

exor D5 exor D7 C2 is a parity check on every

data bit whose position is xx1x C2 D1

exor D3 exor D4 exor D6 exor D7 C4 is a parity

check on every data bit whose position is x1xx

C4 D2 exor D3 exor D4 exor D8 C8 is a parity

check on every data bit whose position is 1xxx

C8 D5 exor D6 exor D7 exor D8

Why? Because we want the syndrome, the Hamming

test word, to yield the address of the error.

11

Example

12

Example

Data stored 00111001 Check bits

Putting it together

13

Example

Word fetched

Check bits

Putting it all together

EXORing 0

1 1 0

0110 6 ? bit position 6 is wrong, i.e. bit D3

is wrong

14

SEC-DEC Example Requires One Extra Check Bit

Single Error Correction, Double Error Detection

Single Error Correction

Word With

Even Parity Word

With Even Parity

With Two Errors

With Errors Identifying

Error SEC Attempt

IS SEC Correct? Extra

Bit Confirms DE

15

We will finish Chapter 5 next Tuesday

16

Improvements in memory

- RAM continually gets denser.

- DRAM Several improvements

- SDRAM synchronous DRAM

- DDR-SDRAM - doubles transfer speed

- RDRAM asynchronous one transfer

- per clock cycle

17

Comparison of improved DRAM

Conventional DRAM 40 to 100 MB/S transfer

rate?

18

Synchronous DRAM (SDRAM)

- Access is synchronized with an external clock

- Address is presented to RAM

- RAM finds data (CPU waits in conventional DRAM)

- Since SDRAM moves data in time with system clock,

CPU knows when data will be ready - CPU does not have to wait, it can do something

else - Burst mode allows SDRAM to set up stream of data

and fire it out in block - DDR-SDRAM sends data twice per clock cycle

(leading trailing edge)

19

SDRAM Read Timing

20

SDRAM

21

DDR SDRAM

- SDRAM can only send data once per clock

- Double-data-rate SDRAM can send data twice per

clock cycle - Rising edge and falling edge

22

RAMBUS

- Adopted by Intel for Pentium Itanium

- Main competitor to SDRAM

- Separate bus (hence the name RAMBUS)

- Bus addresses up to 320 RDRAM chips at 1.6Gbps

- Asynchronous block protocol

- Precise control signal timing

- 480ns access time

- Then 1.6 Gbps

23

RAMBUS Diagram