9'4 Clocked CMOSC2MOS - PowerPoint PPT Presentation

1 / 19

Title:

9'4 Clocked CMOSC2MOS

Description:

The clock signal (or clk) is a periodic waveform with a well defined period T ... clock returns to a value = 1. ... so that the clocks overlap slightly during ... – PowerPoint PPT presentation

Number of Views:42

Avg rating:3.0/5.0

Title: 9'4 Clocked CMOSC2MOS

1

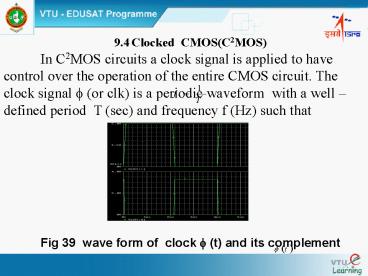

9.4 Clocked CMOS(C2MOS) In C2MOS circuits

a clock signal is applied to have control over

the operation of the entire CMOS circuit. The

clock signal ? (or clk) is a periodic waveform

with a well defined period T (sec) and

frequency f (Hz) such that

Fig 39 wave form of clock ? (t) and its

complement

2

During this interval, the FET logic arrays are

not connected to the output, so the inputs have

no effect. Instead, the output voltage is held on

Cout until the clock returns to a value ? 1.

Fig.40 Structure of C2MOS gate Fig.41 Circuit of

NAND2 gate Fig.42 Circuit of NOR2 gate

3

If ? (t) is defined to have a minimum value of 0

V and a maximum of VDD, then so that the

clocks overlap slightly during a transition. It

may be advantageous to create a set of clocks

that are truly non-overlapping for all times.

The general structure of a C2MOS gate is shown in

fig.40. It is composed of a static logic circuit

with tri-state output network made up of FETs

M1 and M2 that is controlled by ? and .

4

When ? 1, both M1 and M2 are active. Since both

the pFET and nFET logic blocks are connected to

the output node, the circuit degenerates to a

standard static logic gate. The output f(a,b,c)

is valid during this time, establishing the

voltage Vout on the output capacitance Cout. When

the clock changes to a value ? 0, both M1 and

M2 are in cutoff, so that the output is in

high-impedance state Hi-Z. During this interval,

the FET logic arrays are not connected to the

output, so the inputs have no effect. Instead,

the output voltage is held on Cout until the

clock returns to a value ? 1.

5

Charge sharing thus reduces the output voltage.

To keep Vout high, the capacitors must satisfy

the relation Cout C1 C2.VLSI system is

often complicated by the total power consumption

of a chip.

Advantages 1) The Clock controls the

entire operation of the logic gate.2) New

group of data bits enter the network during every

clock cycle.

6

This affects the choice of packaging, the

intended application (desktop or portable), the

power supply characteristics, and the heat

sinking and cabinet ventilation requirements.

The interplay between system constraints and

the circuit design must always be forced into

the design.

7

A dynamic logic gate uses clocking and charge

storage properties of MOSFETs to implement logic

operations.The clock provides synchronized data

flow which makes the technique useful in

designing sequential networks. They are based on

the circuit illustrated in fig.43. The clock ?

drives a complimentary pair of transistors Mn and

Mp these control the operation of the circuit

and provide synchronization.

9.5 Dynamic CMOS logic

Circuits

8

Disadvantages of Clocked CMOS(C2MOS) Circuit

1) Output node cannot hold the charge on Vout

for a very long time due to phenomenon called

charge leakage. 2) Lower limit on the clock

frequency will be laid by the phenomenon of

charge leakage. This makes the operation of the

logic to be done at lower frequency range only.

9

Fig.43 Basic Dynamic Logic gate

Logic is implemented using an nFET

array between the output node and ground.

The output voltage Vout is taken across the

output capacitor Cout.

10

The transistor arrays are designed using the same

technique as for standard logic gates. The

circuits of a NAND2 and NOR2 are shown fig.41 and

fig.42 respectively. The presence of the

series-connected clocking FETs automatically

lengthens both the rise and fall times of the

circuit.

11

A clock transition to ? 1 drives the circuit

into the evaluation mode where Mp is off and Mn

is on. The inputs are valid and control the

switching in the nFET logic array Mn is usually

called the evaluate transistor. If the logic

block acts like a closed switch, then Cout can

discharge through the logic array and Mn this

gives the final result of Vout 0 V,

corresponding to a logic f 0.

12

The clocking signal ? defines two distinct modes

of operation during every clock. When ? 0,

the circuit is in PRECHARGE with Mp and Mn off.

This establishes a conducting path between VDD

and the output, allowing Cout to charge voltage

Vout VDD. Mp is often called the precharge FET.

Since the bottom of the nFET logic block is not

connected to ground during precharge, the inputs

have no effect.

13

valid only during the evaluation period when ?

1.

A dynamic NAND3 circuit is shown in fig.43. Logic

formulation is achieved using the three

series-connected FETs. The output f a.b.c is

Fig.43 Circuit of Dynamic NAND3 Fig.44 Charge

Sharing Circuit

14

Since the evaluation nFET is in series with the

logic block, Cout must discharge through four

transistors. Increasing the sizes of the nFETs

will reduce the fall time. Charge leakage reduces

the voltages held on the output node when f 1.

Another problem called CHARGE SHARING can

occur when the clock makes a transition to It

has the effect of reducing the output voltage

even before charge leakage effects become

noticeable.

15

The origin of the charge sharing problem is the

parasitic node capacitance C1 and C2 between FETs

as shown in Fig.44. The clock has been set at ?

1 so that Mp is off, isolating the output

node from the power supply. The initial voltage

on Cout at the start of the evaluation interval

is Vout VDD as shown. Assuming that the

capacitor voltages V1 and V2 are both 0 V at this

time, the total charge on the circuit is Q Cout

VDD.

16

The current I flows because Vout is initially

larger than V1 or V2. This corresponds to the

transfer of charge from Cout to both C1 and C2.

The current flow ceases when the voltages

are equal with a final value Vout V1

V2 Vf. The total charge on the circuit

is then distributed according to Q Cout Vf

C1 Vf C2 Vf (Cout C1 C2) Vf

17

The worst case charge sharing condition for this

circuit is when the inputs are (a,b,c) (1,1,0).

With c 0, there is no discharge path to

ground, so that the output voltage should remain

high. However, since the a- and b- input FETs

are on, Cout is electrically connected to C1 and

C2 as indicated by the darkened lines.

18

If the inputs cause the block to behave like and

open switch from top to bottom, the charge on

Cout is held and Vout VDD logically, this is

an output of f 1. Charge leakage eventually

drops the output to which would be an incorrect

logic value. The hold time is determined by the

circuitry. In general, this consideration places

a minimum frequency stipulation on the clock.

19

Applying the principle of conservation of charge,

this must be equal to the initial charge in the

system Q (Cout C1 C2) Vf Cout VDD

Solving for the final voltages

gives Sincewe see that Vf lt VDD